# **Prime DC/AC Buck-Boost Converter**

Derivation of mathematical models and evaluation of lumped transmission lines with focus on size and efficiency

Master of Science Thesis

## Mike Kiprianoff

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2012

# **Prime DC/AC Buck-Boost converter**

Derivations of mathematical models and evaluation of lumped transmission lines with focus on size and efficiency

Mike Kiprianoff

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2012

Prime DC/AC Buck-Boost converter Derivations of mathematical models and evaluation of lumped transmission lines with focus on size and efficiency Mike Kiprianoff

© Mike Kiprianoff, 2012

Department of Energy and Environment Division of Electric Power Engineering Chalmers University of Technology SE–412 96 Göteborg Sweden Telephone +46 (0)31–772 1000

Cover: A picture of a Prime Buck-Boost converter prototype.

Chalmers Bibliotek, Reproservice Göteborg, Sweden 2012

Prime DC/AC Buck-Boost converter Derivations of mathematical models and evaluation of lumped transmission lines with focus on size and efficiency Mike Kiprianoff Department of Energy and Environment Division of Electric Power Engineering Chalmers University of Technology

#### Abstract

Introducing a transmission line into the fundamental power conversion circuits (Buck, Boost and Buck-Boost) has given the possibility to create converters types with new properties. A modified Buck-Boost converter in DC/AC operation has been evaluated. The main goal was to verify if a DC/AC conversion could be made and to optimize its efficiency with different lumped transmission lines (LTL). The idea was to decrease the total area of the LTL in order to make the solution more attractive for the power electronic market. Moreover, there was no theoretical explanation of the converter. Therefore the transfer function was investigated and a mathematical explanation of the converter was provided.

The converter works in two different modes, inverting and non-inverting. In its inverting mode it works as a regular Buck-Boost converter and in its non- inverting mode it can provide an output voltage with the same polarity as the input voltage. The current and voltage wave propagating inside the LTL can be described with general microwave theory. The converter was also proven to work in DC/AC mode and has an efficiency of 69% with a LTL with U-core inductors. The efficiency can be interpreted as low since old measurements with an LTL incorporating surface mounted inductors instead, showed an efficiency of 81%. The decrease in efficiency is most likely due to a malfunctioning MOSFET. In non-inverting mode the efficiency was increased with two of the U-core LTLs. The Prime Buck-Boost solution has great potential, but at the moment the efficiency is too low and the total area is too big. An investigation of the converter in AC/DC mode with GaN switches and LTLs with E-cores has been proposed for future work.

**Index Terms:** Buck Boost, Buck/Boost, Buck-Boost, Converter, Transmission Line, Lumped Transmission Line, Wave propagation, Power Electronic Converter.

## Acknowledgements

First and foremost, I would like to thank the innovative and knowledgeable Sverker Sander for technical support during the thesis.

Secondly, I would like to thank Andreas Karvonen and Torbjörn Thiringer for feedback and guidance with thesis writing.

Finally, I want to thank Ericsson Lindholmen in Göteborg and the unit Board Power for supplying resources, such as components, instruments and financial support during the project.

Mike Kiprianoff Göteborg, Sweden, 2012

## **List of Symbols**

$\Delta_1$ -  $\Delta_4$  – Different time intervals in non-inverted mode.

$\Delta v_{c}$  – Voltage difference when load capacitor is charged

$\Delta x$  – Time interval between chosen reflections.

$\gamma$  – Propagation constant

$\eta$  – Efficiency

$\eta_{PwSt}$  – Power stage Efficiency

$\Gamma_g$  – Reflection coefficient at generator

$\Gamma_L$  – Reflection coefficient at S<sub>C</sub> when it's on

$\Gamma_{L1}$  – Reflection coefficient at S<sub>C</sub> when it's off

$\Gamma_{L2}$  – Reflection coefficient at load

C – Capacitance

d – Transmission line length

D - Duty cycle

G – Conductance

$fr_1$  – First resonance frequency

$f_{sw}$  – switch frequency

$I_1^+$  - Initial current wave propagating in a TL

$I_5^+$  - Current amplitude when interval  $\Delta_4$  begin

$I_{\rm L}$  – Load current

$I_{SA}$  – Current at switch  $S_A$

$I_{\rm SC}$  – Current at switch S<sub>C</sub>

l – Inductance per meter

L-Inductance

L'- Total inductance of a shorted TL below its resonance frequency

M – Number of reflections

N – Number of LC elements

$N_{\Gamma g}$  – Number of reflections at S<sub>A</sub> during interval  $\Delta_1 - \Delta_2$

$N_{\Gamma L}$  – Number of reflections at S<sub>C</sub> during interval  $\Delta_1 - \Delta_2$

$N_{\Gamma L1}$  – Number of reflections at S<sub>C</sub> during interval  $\Delta_3 - \Delta_4$

$N_{\Gamma L2}$  – Number of reflections at load during interval  $\Delta_3 - \Delta_4$

$P_{\rm drv}$  – Driver power

$P_{\rm iso}$  – Isolator power

$P_{\rm in}$  – Input power

$P_{\rm out}$  – Output power

$P_{PwSt}$  – Powerstage power

R-Resistance

S-Switch

$S_{\rm A}$  – High- side switch

$S_{\rm B}$  – High- side switch for synchronous rectification

$S_{\rm C}$  – Low-side switch for non- inverting operation

$t_{\rm d}$  – Delay time in TL

$T_{\rm S}$  – Period time

*V* - Voltage wave when interval  $\Delta_2$  begin

$V_1^+$  - Initial voltage wave propagating in a TL

- $V_2^+$  Second voltage wave propagating in a TL after reflection

- $V_{\rm IN AC}$  AC input voltage

- $V_{\rm in} DC$  input voltage  $V_{\rm out} Output voltage$

- $V_{\rm rect}$  Rectified voltage

- $X_{\rm L}$  Inductive reactance

- z' Transmission line position

- $Z_0$  Characteristic impedance

- $Z_{\rm L}$  Load impedance  $Z_{\rm in}$  Generator input impedance

## Abbreviations

| AC     | Alternating Current                               |

|--------|---------------------------------------------------|

| DC     | Direct Current                                    |

| DCR    | Direct Current Resistance                         |

| ESR    | Equivalent Series Resistance                      |

| GaN    | Gallium Nitride                                   |

| LTL    | Lumped Transmission Line                          |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PBB    | Prime Buck-Boost                                  |

| PCB    | Printed Board Circuit                             |

| PRIME  | PropagatIon MEdium                                |

| PPC    | Prime Power Conversion                            |

| RMS    | Root Mean Square                                  |

| TL     | Transmission Line                                 |

# Contents

| Abst | tract. |                                             | iii |

|------|--------|---------------------------------------------|-----|

| Ackı | nowle  | edgements                                   | V   |

| List | of Sy  | mbols                                       | vii |

| Abb  | revia  | tions                                       | ix  |

| Cont | tents  |                                             | xi  |

| 1    | Intro  | oduction                                    |     |

| _    | 1.1    | Problem Description                         |     |

|      | 1.2    | Purpose                                     |     |

|      | 1.3    | Objectives                                  |     |

|      | 1.4    | Previous Work                               | 3   |

| 2    | Tech   | nical Background                            | 5   |

|      | 2.1    | AC/DC Conversion with Prime Buck-Boost      |     |

|      | 2.2    | Transmission Line Theory                    |     |

|      | 2.3    | Transients on a transmission line           |     |

|      | 2.4    | A Principle of Energy Accumulation in a TL  |     |

|      | 2.5    | Non-inverting Operation of Prime Buck-Boost |     |

| 3    | Prim   | e Buck-Boost DC/AC Simulation               | 15  |

|      | 3.1    | LTL Simulation                              | 15  |

|      | 3.2    | Efficiency                                  |     |

|      | 3.3    | Decrease and Increase of LC elements        |     |

|      | 3.4    | DC/AC Function                              |     |

| 4    | Matl   | hematical Model                             |     |

|      | 4.1    | Transients in Non- inverting Operation      |     |

|      |        | 4.1.1 Interval $\Delta_1$                   |     |

|      |        | 4.1.2 Interval $\Delta_2$                   |     |

|      |        | 4.1.3 Interval $\Delta_3$                   |     |

|      |        | 4.1.4 Interval $\Delta_4$                   |     |

|      | 4.2    | Transfer Function                           |     |

|      |        | ctance Design and Measurement               |     |

|      | 5.1    | Equipment                                   |     |

|        | 5.2    | Measurements                                          |    |

|--------|--------|-------------------------------------------------------|----|

|        |        | 5.2.1 Coilcraft Inductance                            |    |

|        |        | 5.2.2 U-core Air Gap Adjustment                       |    |

|        |        | 5.2.3 Ferrite U-core Inductance                       |    |

|        |        | 5.2.4 Ferrite Toroidal Core Inductance                | 34 |

| 6      | LTL    | Impedance Measurement                                 | 37 |

|        | 6.1    | Equipment                                             |    |

|        | 6.2    | Measurement Setup                                     |    |

|        | 6.3    | Measurements                                          |    |

| 7      | Effici | iency Optimization                                    | 43 |

|        | 7.1    | Measurement Setup                                     |    |

|        |        | 7.1.1 Equipment                                       | 45 |

|        | 7.2    | Measurements                                          | 45 |

|        |        | 7.2.1 LTL delay time                                  | 46 |

|        |        | 7.2.2 Switch Frequency                                | 47 |

|        |        | 7.2.3 Input Voltage                                   | 47 |

|        |        | 7.2.4 Switch $S_{\rm C}$ Off Time                     | 48 |

|        |        | 7.2.5 Dead Time for Switch $S_A$ and $S_B$            | 49 |

|        |        | 7.2.6 Efficiency Non- Inverting Operation             | 50 |

|        | 7.3    | Increase of LC Elements                               | 51 |

|        | 7.4    | Double <i>S</i> <sub>C</sub> switching                | 53 |

| 8      | Prime  | e Buck-Boost DC/AC Function                           |    |

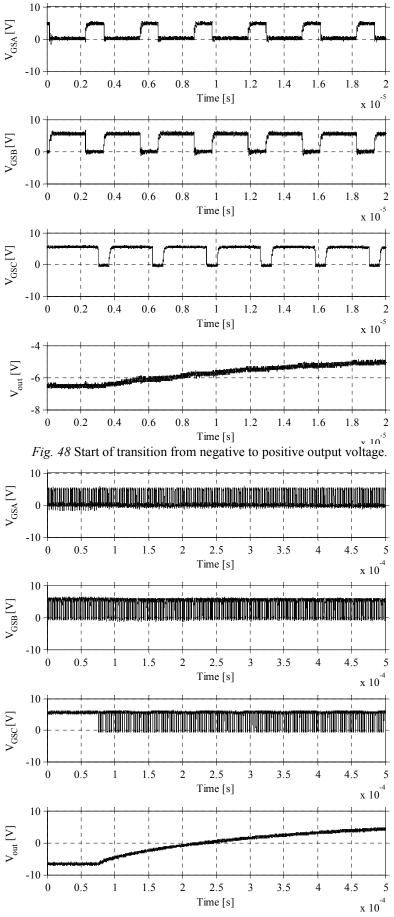

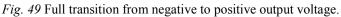

|        | 8.1    | Transition from Negative to Positive Output Voltage   |    |

|        | 8.2    | Low Frequency AC Modulation of Output Voltage         |    |

|        | 8.3    | <i>V</i> <sub>out</sub> as a Function of Duty Cycle   | 58 |

| 9      | Conc   | lusions                                               | 61 |

|        | 9.1    | Future work                                           | 62 |

| 10     | Refer  | ences                                                 | 63 |

| Α      | LTL    | Drawings                                              | 65 |

|        | A.1    | LTL <sub>1</sub>                                      |    |

|        | A.2    | LTL <sub>2</sub>                                      | 66 |

|        | A.3    | LTL <sub>3</sub>                                      | 67 |

|        | A.4    | U-core                                                | 68 |

|        | A.5    | Toroid                                                | 68 |

|        |        |                                                       |    |

| B      | Prime  | e Buck-Boost Schematic                                | 69 |

| B<br>C |        | e Buck-Boost Schematic<br>oved and Changed Components |    |

|        | Remo   |                                                       | 71 |

Е

| Time | Space Diagram for Double $S_{ m C}$ Switching | .75 |

|------|-----------------------------------------------|-----|

| D.4  | LTL <sub>3</sub> , INX 106 781/16 P1A         | .74 |

| D.3  | LTL <sub>2</sub> , INX 106 781/16 P1A         | .73 |

| D.2  | LTL <sub>1</sub> , INX 106 781/16 P1A         | .73 |

## **Chapter 1**

# **1** Introduction

For the last three years, Ericsson has conducted an internal research project regarding power electronic converters utilizing transmission lines. The project is called Prime Power Conversion (PPC) and concerns DC-DC, DC-AC and AC-DC converters. Sverker Sander who is the founder and main executor of the project, had an idea of replacing the inductance, which is normally used as an energy storage device for a power electronic converter, with a transmission line<sup>1</sup> (TL). By introducing a TL into the fundamental power conversion circuits (Buck, Boost and Buck-Boost), new configurations previously not addressed in literature could be made possible [1].

The idea of introducing a TL to accumulate energy within a converter, have been proven to give properties that are not available with conventional converters. Examples of these properties are reduced number of semiconductors, multiple voltage ouputs and if using a Buck-Boost configuration the output voltage can be non-inverted i.e – it has the same polarity as the input voltage. The last example also enables the possibility to build an AC/DC converter with a reduced number of semiconductors [2].

The AC/DC concept is named Prime Buck-Boost (PBB) converter and was realized into a prototype in late 2011. It was tested in a DC/AC configuration and was proven to have a decent efficiency. In order to make the PBB converter more attractive for future work, it continued as this master thesis.

#### **1.1 Problem Description**

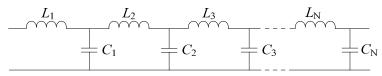

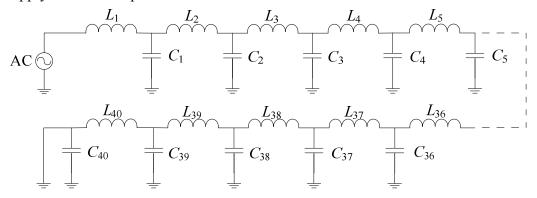

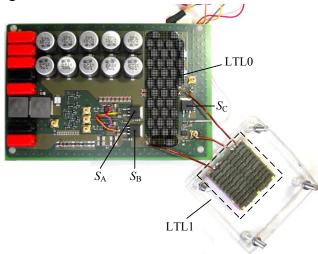

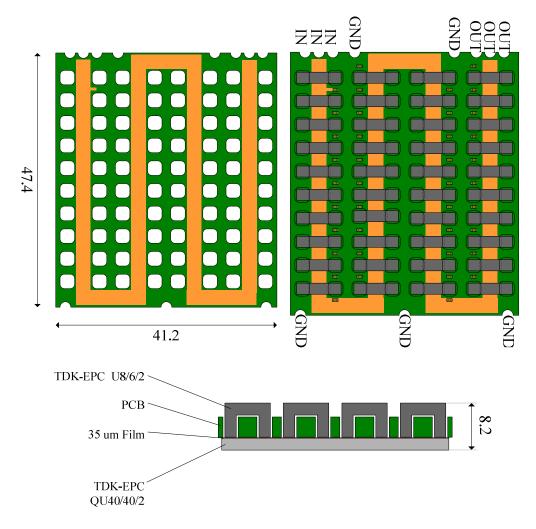

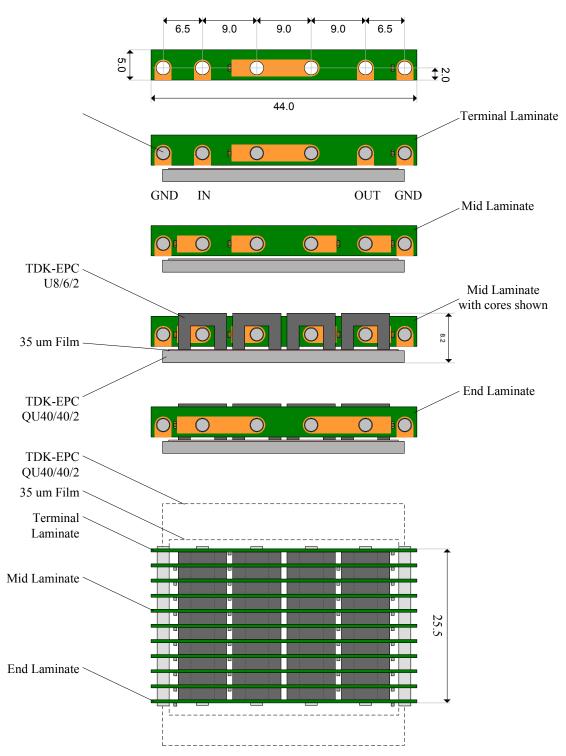

The previous TL in the PBB converter, from now on called lumped transmission line 0 ( $LTL_0$ ), was built with an LC network made of 40 lumped surface mounted inductors and capacitors, see illustration in Fig. 1.

Fig. 1 A lumped LC network illustrating the inductances and capacitors.

<sup>&</sup>lt;sup>1</sup> A transmission line could be some sort of cable; a printed circuit board microstrip or stripline; a delay line or an LC network of lumped inductors and capacitors (LTL) [1].

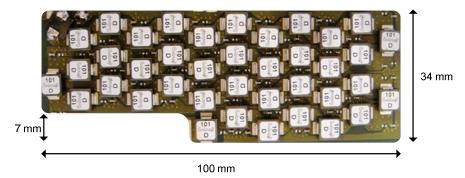

Many power electronic companies compete by decreasing size and component cost of their products;  $LTL_0$  will consequently be hard to implement in a real product due to its size. A decision was made in the PPC project to replace the old LTL in order to reduce its drawbacks, which are;

- 1. Each inductor requires two pads on the PCB top layer to interface its terminals, creating 80 pads in total.

- 2. The inductor building height is 3mm which result in a 'low and wide' LTL distribution with a total size of 30.5cm<sup>2</sup>, see Fig. 2.

- 3. Each inductor can carry a 50A RMS which is oversized for the desired application.

Fig. 2 Size and design of LTL.

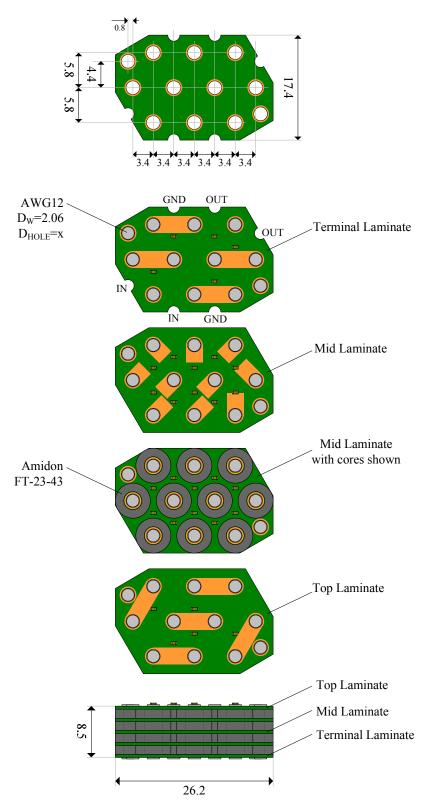

Due to the drawbacks, three new LTLs were designed and produced in parts. These will from now on be called  $LTL_1$ ,  $LTL_2$  and  $LTL_3$ , see Appendix A for dimensions. The difference between them is that the two first uses ferrite U-cores and the third uses ferrite toroidal cores as inductances.  $LTL_0$  was on the other hand made out of 40 surface mounted Coilcraft inductors and 40 Murata capacitors see Table 1 for specification. The capacitors are common for each LTL.

|--|

| Coilcraft<br>SLC7530S-101MLC  | Murata<br>GRM1555C1H561J |

|-------------------------------|--------------------------|

| $L = 100 \pm 20 nH$           | C = 560±5pF              |

| DCR = $0.123 \text{ m}\Omega$ | $ESR = 0.057\Omega$      |

### 1.2 Purpose

To theoretically and practically evaluate a new DC/AC Buck-Boost Converter that features controllable inverting and non-inverting power conversion. It incorporates derivations of mathematical models, optimization of efficiency and electrical verification of lumped transmission lines. The idea is to make the solution more attractive for further development in the power electronic industry.

### 1.3 Objectives

The first objective of this thesis was to finalize the manufacturing of the LTLs and obtain the same impedance for the new LTLs as the old one in order to be able to compare them regarding efficiency. The second goal was to simulate the current magnitude, the efficiency and the DC/AC conversion of the PBB converter. The third objective was to practically optimize and increase the converter efficiency with the new LTLs and to verify the DC/AC conversion. Finally there was no theoretical explanation of the converter transfer function. Therefore, the fourth objective was to investigate the transfer function and provide a theoretical explanation of how the converter operates.

#### **1.4 Previous Work**

Transmission lines have long been used in radio frequency applications in order to shape waveforms and improve efficiency [3]-[4]. A transmission line which is open- or short circuited has a certain resonance frequency dependant on the impedance of the line. If the TL is used at a frequency equal to its first resonance frequency it enforces odd- and even harmonics in the voltage and current [3] [5]. By the use of transmission lines in high frequency power conversion circuits and a switch frequency equal or close to the first resonance frequency, new power conversion properties and/or the possibility to utilize the harmonic content is possible [3]-[11]. Distinguished from these studies, the PPC research project at Ericsson shows solutions were the energy storage device is replaced with a transmission line inside the converter topologies Buck, Boost and Buck-Boost [1]-[2]. As mentioned, the solutions have given the possibility to have multiple voltage outputs, a reduced number of semiconductors and a controllable non-inverting and inverting power conversion. A key thing in the project has been the use of switch frequencies an order of magnitude lower than the first resonance frequency [2]. The same switch principle is used for the PBB converter in this master thesis.

## Chapter 2

# 2 Technical Background

This section discusses the Prime Buck-Boost converter, general transmission line theory, the basic idea of energy accumulation in a TL and how the non-inverting function is possible with the converter.

#### 2.1 AC/DC Conversion with Prime Buck-Boost

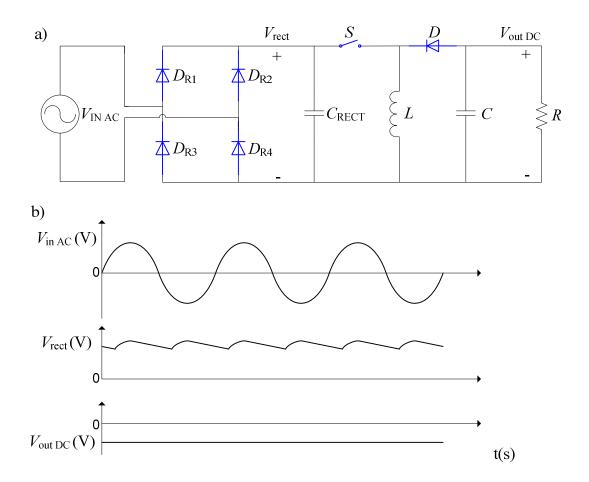

A common technique to do an AC/DC conversion is to use a full wave diode rectifier followed by a converter, see Fig. 3a. In this example, the converter is a Buck-Boost converter. The conversion is achieved by a high side switch S. When S is on, energy is accumulated within the inductance L and the capacitor C supplies the load with energy. When S is off, the inductor supplies R and C with energy, due to a free-wheel current from L through R, C and the diode D. It can further be noted that the transfer function of a regular Buck-Boost converter is

$$\frac{V_{\text{out}}}{V_{\text{rect}}} = \frac{-D}{1-D} \tag{1}$$

where  $V_{out}$  is the output voltage,  $V_{rect}$  the rectified voltage and D the duty cycle. This means that  $|V_{out}|$  can either be increased or decreased compared to  $V_{rect}$ , with the side-effect that the voltage polarity is inverted, see Fig. 3b [12].

*Fig. 3* A simplified circuit diagram for a full bridge rectifier followed by a Buck-Boost converter with typical voltage waveforms.

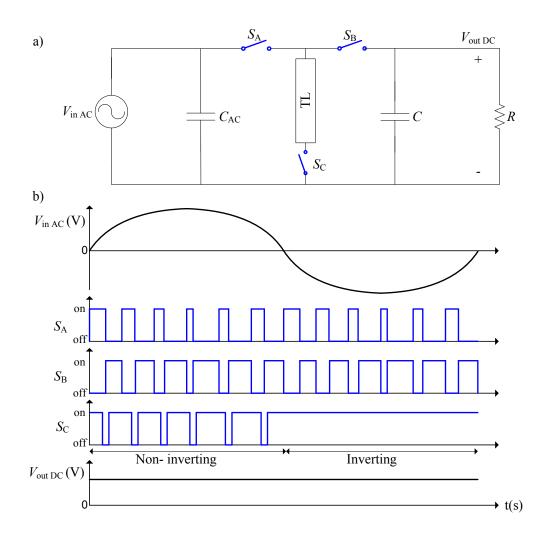

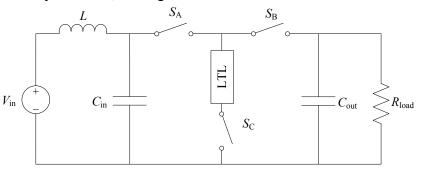

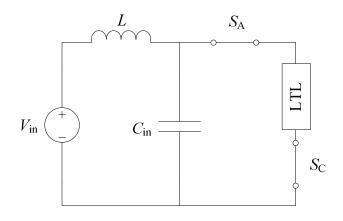

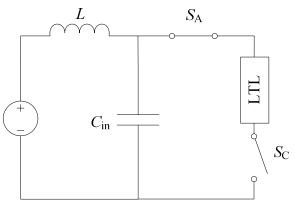

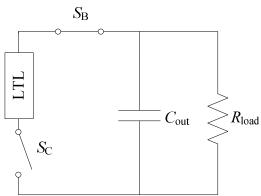

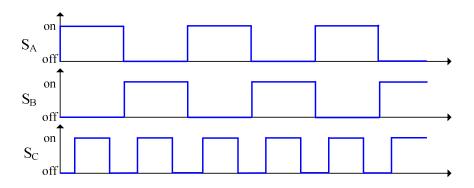

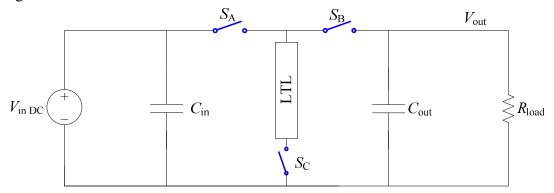

The PBB idea was to create an AC/DC- conversion with only three semiconductors, achieving the same result as the above. The difference between a regular Buck-Boost and the PBB converter is that the inductor is replaced with a transmission line and the diode with a switch  $S_B$ . There is also an added switch  $S_C$  at the end of the TL, see Fig. 4a.

In order for an AC/DC- conversion to be possible, it implies that the converter can both have positive and negative output voltage regardless of the input voltage polarity. This is achieved with switch  $S_C$ . The basic idea is that if  $S_C$  is continuously on and  $S_A$  and  $S_B$  are switched sequentially, the circuit works as a regular Buck-Boost converter. If  $S_C$  is briefly opened instead, the output polarity retains the same as the input, see Fig. 4b. Exploiting this fact, enables the converter to work in two operations modes, inverting and non-inverting. This gives the possibility to do a full wave rectified AC/DC- conversion incorporating only three semiconductors.

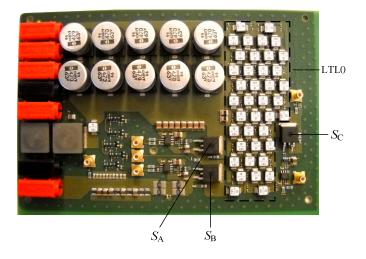

*Fig. 4* The Prime Buck-Boost converter and the modulation technique for the different switches in order to achieve AC/DC conversion.

For the AC/DC- conversion to work, it implies that switch  $S_A$  and  $S_B$  block both positive and negative drain-source voltages. The most common switch in the low voltage power electronic industry is the MOSFET. The drawback with regular power MOSFETs is that they have an intrinsic body diode between drain and source. Normally it causes no problems, since the voltage blocking polarity is constant. But when using MOSFETs in a PBB AC/DC- conversion, they will be exposed to both positive and negative voltage which will cause a short-circuit. It exist switches without body diodes. One type that offers this property is called GaN switches. Unfortunately, these GaN switches were not available during the PBB project. Instead the non-inverting function was tested and verified by building a DC/AC converter circuit with MOSFETS, see Fig. 5. The PBB converter can be seen to be big due to the input capacitors and the total surface of LTL<sub>0</sub>. The big input filter is used to attenuate low frequency 50Hz input current ripple. The placement of components is not optimal either, since it is a prototype. The total size of the converter can therefore be reduced. The converter schematics can be found in appendix B.

Fig. 5 The Prime Buck-Boost converter.

### 2.2 Transmission Line Theory

The telegraph equations can be used to find the voltage and current at a specific point along the transmission line. These can be expressed as

$$V(z') = I_{\rm L}(Z_{\rm L} \cosh \gamma z' + Z_0 \sinh \gamma z'), \qquad (2)$$

$$I(z') = \frac{I_{\rm L}}{Z_0} (Z_{\rm L} \sinh \gamma z' + Z_0 \cosh \gamma z')$$

(3)

with terms of load current  $I_L$ , load impedance  $Z_L$ , propagation constant  $\gamma$  and characteristic impedance  $Z_0$ ,  $\gamma$  and  $Z_0$  can be found as

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)} \tag{4}$$

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \,. \tag{5}$$

Dividing (2) with (3) and inserting the line length z'=l gives

$$Z_{\rm in} = Z(l) = Z_0 \frac{Z_L + Z_0 \tanh \gamma l}{Z_0 + Z_L \tanh \gamma l}$$

(6)

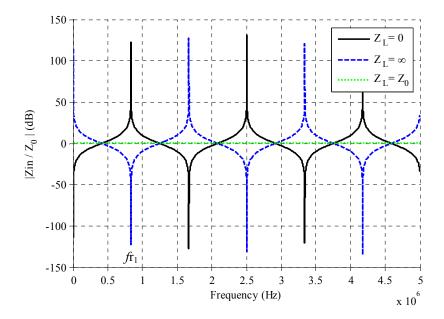

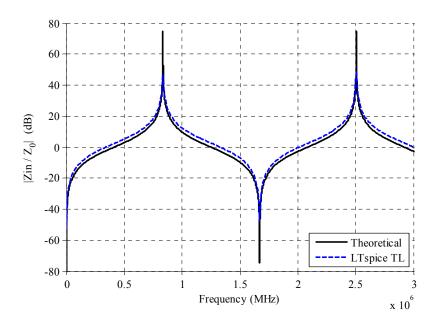

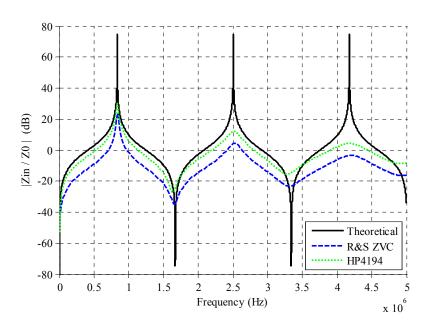

where  $Z_{in}$  is the input impedance the generator sees when looking into the line [13]. The input impedance is plotted in Fig. 6 with respect to frequency for short circuit, open and terminated load. L and C are set to 100nH and 560pF (the Coilcraft and Murata component values used in LTL<sub>0</sub>). In this case, the line is considered lossless (R and G are zero).

Fig. 6 Theoretical input impedance with different load impedance Z<sub>L</sub>.

As seen, the impedance has several resonance frequencies. The first resonance can be found as

$$f\mathbf{\hat{r}}_1 = \frac{1}{4N\sqrt{LC}} \tag{7}$$

where N is the number of combined LC elements [5]. For the case of 40 LC elements in  $LTL_0$ , the first resonance frequency  $fr_1$  becomes 835kHz. This can also be seen in Fig. 6.

### 2.3 Transients on a transmission line

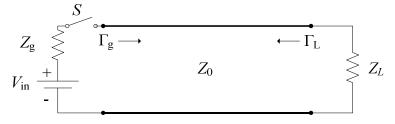

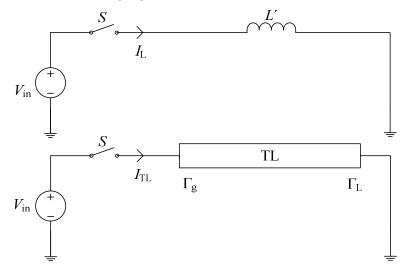

In the simplest case, a DC- voltage source  $V_{in}$  is applied through a series internal impedance  $Z_g$  to a lossless transmission line, see Fig. 7. It has the characteristic impedance  $Z_0$  and load impedance  $Z_L$ . The reflection coefficients are denoted  $\Gamma_g$  at the input end and  $\Gamma_L$  at the output end.

Fig. 7 A DC- source applied to a transmission line.

When the switch S is closed at time t = 0, a voltage wave of magnitude

$$V_1^+ = \frac{Z_0}{Z_0 + Z_g} V_{\rm in}$$

(8)

and a current wave of magnitude

$$I_{1}^{+} = \frac{V_{\rm in}}{Z_{0} + Z_{\rm g}} \tag{9}$$

will travel towards the load. If  $Z_L \neq Z_{0,}$  the wave will be reflected at time t = t<sub>d</sub> and travel back to the DC- source with a magnitude of

$$V_{1}^{-} = \Gamma_{L} V_{1}^{+} \tag{10}$$

where the reflection coefficient ( $\Gamma_L$ ) is defined as

$$\Gamma_{\rm L} = \frac{Z_{\rm L} - Z_{\rm 0}}{Z_{\rm L} + Z_{\rm 0}} \,. \tag{11}$$

If  $Z_g \neq Z_0$  the wave will be reflected once again at time  $t = 2t_d$  according to

$$V_2^{+} = \Gamma_L \Gamma_g V_1^{+} \tag{12}$$

where

$$\Gamma_{\rm g} = \frac{Z_{\rm g} - Z_{\rm 0}}{Z_{\rm g} + Z_{\rm 0}} \tag{13}$$

is the reflection coefficient at the generator side.

The waves will reflect at each end at  $t = nT_d$  where n is an integer (1, 2, 3 ... n). This will occur infinitely if the transmission line is lossless. The voltage across the load can then be written as

$$V_{\rm L} = V_1^{+} (1 + \Gamma_{\rm L} + \Gamma_{\rm L} \Gamma_{\rm g} + {\Gamma_{\rm L}}^2 \Gamma_{\rm g} + {\Gamma_{\rm L}}^2 {\Gamma_{\rm g}}^2 + \dots + {\Gamma_{\rm L}}^{\rm n} {\Gamma_{\rm g}}^{\rm n-1} + {\Gamma_{\rm L}}^{\rm n} {\Gamma_{\rm g}}^{\rm n})$$

(14)

and the load current as

$$I_{\rm L} = I_{\rm 1}^{+} (1 - \Gamma_{\rm L} + \Gamma_{\rm L} \Gamma_{\rm g} - \Gamma_{\rm L}^{2} \Gamma_{\rm g} + \Gamma_{\rm L}^{2} \Gamma_{\rm g}^{2} - \dots - \Gamma_{\rm L}^{n} \Gamma_{\rm g}^{n-1} + \Gamma_{\rm L}^{n} \Gamma_{\rm g}^{n})$$

[13]. (15)

These two equations can be used to theoretically explain the current and voltage in the PBB converter LTL.

#### 2.4 A Principle of Energy Accumulation in a TL

Consider the two circuits in Fig. 8 which both have a DC- voltage source connected at the input with a switch S and with its ends grounded. The difference between the circuits is the energy storage device. One uses an inductance L' and the other uses a transmission line (TL).

Fig. 8 Circuit diagrams for a voltage step response analysis of a TL and an inductor L.

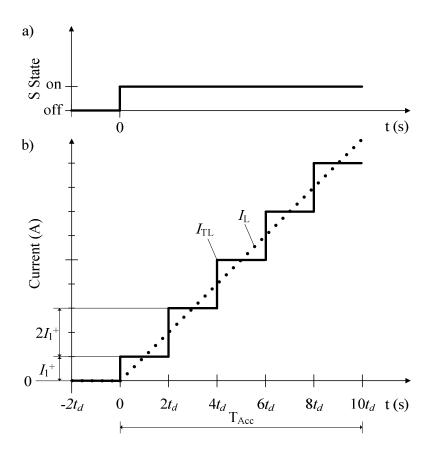

If S is closed at t = 0, a DC-voltage is applied to the inductor and the current  $I_L$  will increase linearly, see Fig. 9. If the same procedure is repeated with a TL, the current  $I_{TL}$  will increase stepwise. This is because of the reflection coefficients  $\Gamma_L$  and  $\Gamma_g$  become -1 since  $Z_L = Z_g = 0$ . Using these values in (15) shows that the current increases immediately by  $I_1^+$  when S is closed and by  $2I_1^+$  every  $2t_d$ .

If a long accumulation interval  $T_{acc}\xspace$  is allowed, the TL can be modeled as an inductor according to

$$L' = dl \tag{16}$$

where d is the TL length in meters and l the inductance per meter. If an lumped transmission line is used, the inductance can be expressed as

$$L' = NL \tag{17}$$

where N is the amount of LC elements and L is the inductance of one L element [1].

*Fig. 9* Accumulation of energy in a TL and inductance L. a) Represent the switch state. b) Shows the currents as a function of time.

### 2.5 Non-inverting Operation of Prime Buck-Boost

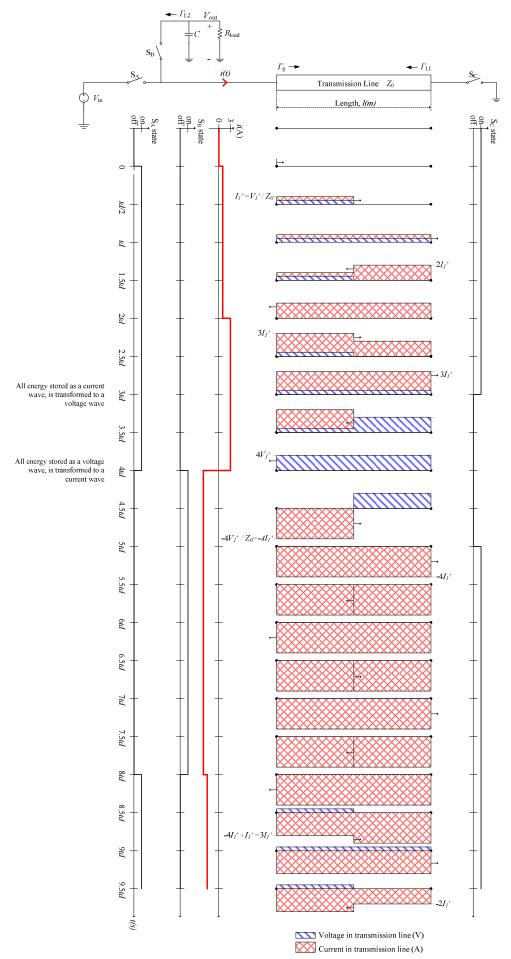

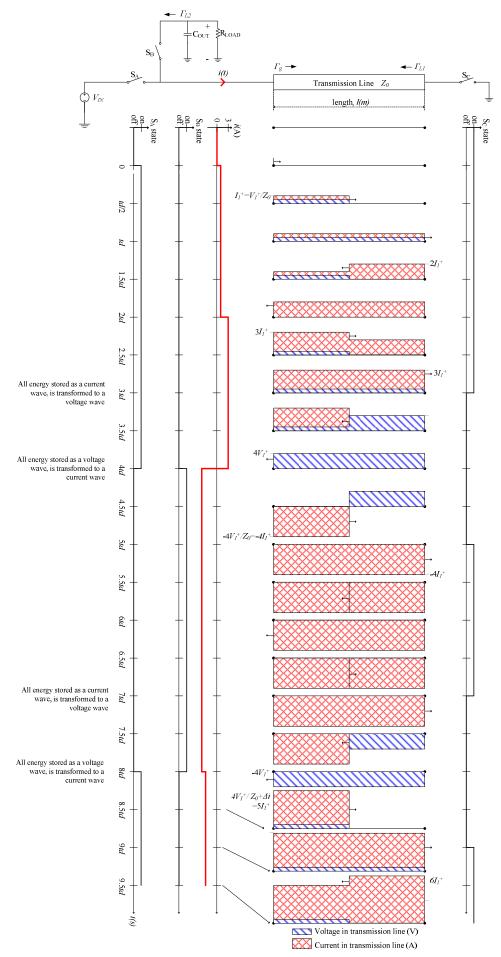

Using the theory above makes it possible to explain the operation cycle for a lossless PBB converter in DC/AC conversion mode. The first operation cycle can be found in Fig. 10. The current (cross-hatched) and voltage waves (hatched) are plotted as a function of to a vertical time axis t(s) and the switch states for  $S_A$ ,  $S_B$  and  $S_C$ . Furthermore, the duty cycle is set to 50% in this example.

#### t=0

Start up of PBB Converter. The Switches  $S_A$  and  $S_C$  are conducting whereas a voltage wave  $V_1^+$  (hatched) and a current wave  $I_1^+ = V_{in/Z_0}$  (crosshatched) will start to propagate along the line.

#### t=t<sub>d</sub>

The waves have reached the TL output end where the reflection coefficient  $\Gamma_{L1}$  is equal to -1 since the TL output end is short circuited. Consequently, according to (14) and (15), the voltage wave will be reflected into  $V_1^-$  with inverted polarity and the current wave polarity remains unchanged. The sum of  $V_1^-$  and  $V_1^+$  becomes zero and the current increases to  $2I_1^+$ .

#### $t=2t_d$

The waves have reached the TL input end. The input filter is assumed to have a low impedance compared to the characteristic impedance which result in a reflection coefficient  $\Gamma_g$  close to -1. The current at the input side is increased to  $3I_1^+$  and a new voltage wave equal to  $V_1^+$  will start to propagate towards the TL output.

This procedure between  $0 \le t \le 2t_d$  can be repeated several times to accumulate energy in the TL. However, to limit the size of the graph the total energy accumulation interval was set to  $4t_d$  (the time interval  $S_A$  is on).

#### t=3t<sub>d</sub>

The waves reach the TL output end once again. Switch  $S_A$  is still conducting and  $S_C$  is turned off, thus creating an open termination. The impedance at the output end becomes infinite and no current will flow through  $S_C$ . All energy stored as a current wave in the TL, is transformed to a voltage wave equal to  $4V_1^+$ . The reflection coefficient  $\Gamma_{L1}$  becomes 1 and the voltage wave is reflected with unchanged polarity. This process is considered the core event of the converter's non-inverting operation.

#### $t=4t_d$

At this time instance, the positive voltage wave reaches the TL input. Switch  $S_A$  is turned off,  $S_B$  is turned on and  $S_C$  is still conducting. Thus, the capacitor  $C_{out}$  and the load  $R_{load}$  is connected to the TL input end. At this time instant, the voltage wave begin to transform into a current wave, equaling  $-4V_1^+ / Z_0$ . The current wave propagates towards the TL output end with negative polarity. This is due to that the reflection coefficient  $\Gamma_{L2}$  becomes -1 because of the load  $Z_L$  ( $R_{load}$  parallel to  $C_{out}$ ) is assumed to be much lower than the characteristic impedance of the TL.

#### $t=5t_d$

The voltage wave is completely transformed to a current wave and switch  $S_C$  is turned on again. The current wave reaches the TL output and will be reflected with the same condition as described in time instance  $t=t_d$ . At the same time, until switch  $S_B$  is turned off, the energy stored in the TL will partially charge the output capacitor  $C_{out}$  to a positive voltage (not shown).

It can also be noted that switch  $S_C$  is kept in off state a total time of  $2t_d$ , the time it takes for the wave to propagate back and forth along the TL. This is because of the waves need to have enough time to convert and invert between  $3t_d < t < 5t_d$ . If  $S_C$ conducts less than  $2t_d$ , a part of the wave will be non-inverted and will be added to the inverted wave. The magnitude of the current will therefore be decreased and result in a lower converter efficiency.

#### $t=8t_d$

The operation cycle starts over and Switch  $S_A$  is turned on and  $S_B$  is turned off. If the operation cycle is repeated several of times it will eventually lead to steady state. This means that the converter convert the input DC voltage to an output DC voltage with the same polarity which depend on the duty cycle.

Fig. 10 Time space diagram of the voltage and current waves in the converter.

## **Chapter 3**

# **3 Prime Buck-Boost DC/AC Simulation**

A first simulation of the  $LTL_0$  was performed to investigate how the input impedance  $Z_{in}$  depends on frequency. The idea was to see how well the simulation software LTspice correspond to the transmission line theory. Secondly a simulation of the PBB converter in non-inverting operation was made to investigate efficiency and how  $V_{out}$  depends on duty cycle. Furthermore, a simulation of the PBB converter in DC/AC configuration was made in order to evaluate the efficiency and the DC/AC functionality.

#### 3.1 LTL Simulation

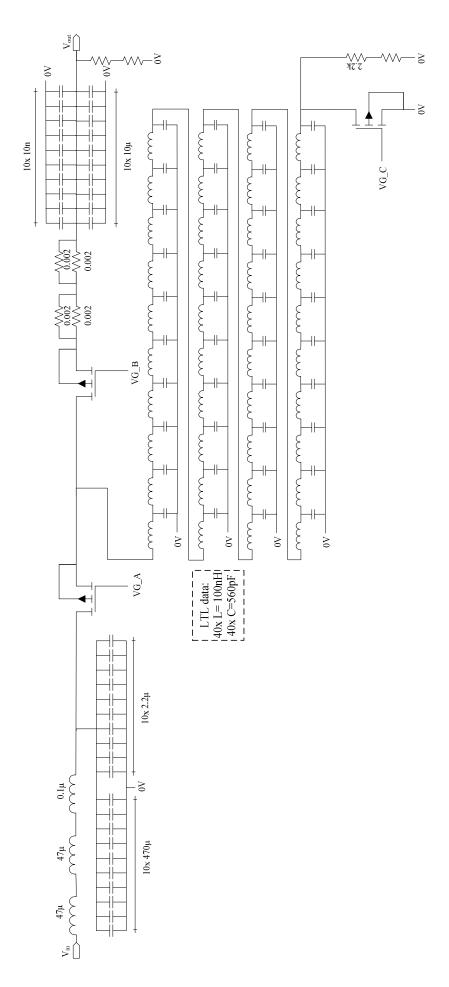

A simulation model of 40 L and C elements, with the same values as the original  $LTL_0$  was implemented, see Fig.11. The LTL simulation was performed to verify the transmission line theory for the LTL input impedance. The input voltage is an AC supply. The AC amplitude was set to 1V.

Fig.11 Simulation setup.

The simulated LTL and a theoretical TL derived from (6), where L and C were set to the same value as in the simulation, can be seen in Fig. 12. The simulated LTL coincide well with the transmission line theory.

*Fig. 12* The theoretical and simulated input impedance as a function of frequency and independent of characteristic impedance.

#### 3.2 Efficiency

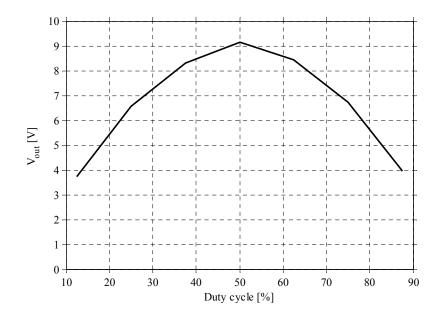

A simulation of the PBB converter with  $LTL_0$  was made in LTspice to see how high the efficiency could be, see Fig. 13.

Fig. 13 Simplified model of the simulated DC/AC Buck-boost converter with a LTL.

The input filter and output filter was set according to the values in the PBB converter, see Table 2. The MOSFETS in the converter was modeled as switches with  $R_{\text{DSon}}=28\text{m}\Omega$ ,  $R_{\text{DSoff}}=10\text{M}\Omega$ , and threshold voltage  $V_t=0.5\text{V}$ . The input voltage was set to 14V. The switch frequency was adjusted until the highest efficiency was achieved. Test simulations in non- inverting mode showed a decrease in efficiency with a duty cycle lower or higher than 50%. Therefore, for the non- inverting mode, it was decided to record the efficiency when the output voltage corresponded to 50% of  $V_{\text{in}}$  at 50 % duty cycle. For inverting mode, the output voltage could not be set to 50% of  $V_{\text{in}}$ . The reason is because of the load resistance would become too small,

which result in a high current in the LTL that saturates the inductors. Therefore, for the inverting mode, the efficiency was simulated with 50% duty cycle and a load of  $6\Omega$  which resulted in an input current of approximately 2.4A in the LTL. The efficiency was 93.4% and for the non- inverting mode it was 90.5 % at a switch frequency of 278kHz.

| In                                                                                                                                             | Output filter                                                       |                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| L                                                                                                                                              | $C_{\rm in}$                                                        | $C_{ m out}$                                                                                               |

| $\begin{array}{c} 2x \text{ Vishay} \\ \text{IHLP-6767GZ-11} \\ \text{L=4.7} \mu\text{H} \\ \text{DCR} = 40.7 \Omega \end{array}$              | 10x Nippon<br>EMVY630ADA471MLH0S<br>C=470μF<br>ESR=0Ω<br>ESL=7nH    | 10x Murata<br>GRM2195C1H103J<br>C=10nF<br>ESR=0.051Ω<br>ESL=0.53nH                                         |

| $\begin{array}{c} 1x \text{ Coilcraft} \\ \text{SLC7530S-101ML} \\ \text{L=100nH} \\ \text{DCR} = 40.7\Omega \\ \text{Cp=0.018pF} \end{array}$ | 10x Murata<br>GRM32ER72A225K<br>C=2.2μF<br>ESR=0.029Ω<br>ESL=0.98nH | $\begin{array}{c} 5x \ Murata \\ GRM32DR71E106K \\ C=10\mu F \\ ESR=0.023\Omega \\ ESL=0.44nH \end{array}$ |

Table 2 Input and output filter data.

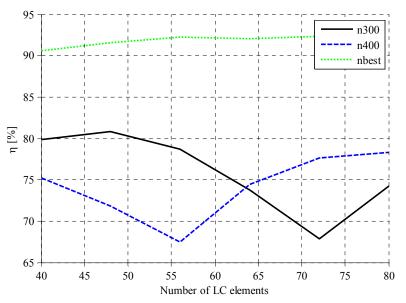

#### **3.3 Decrease and Increase of LC elements**

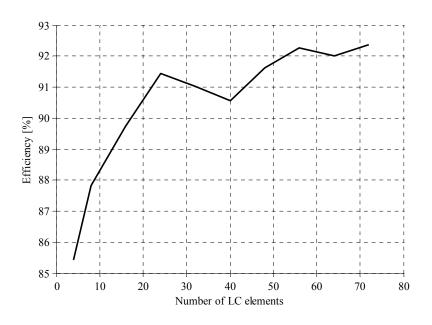

An increase and decrease of LC elements was made in order to see how the efficiency varies. The same simulation setup and procedure as in section 3.2 were used except that the number of elements in the LTL were either decreased or increased with 8 elements at a time.

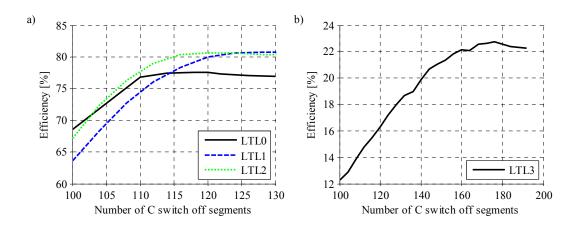

The switch frequency was adjusted as a ratio in the simulation. A ratio of 6 were used, which is the same ratio as the one corresponded to 278kHz for 40 LC elements were used. The reason was to see how the efficiency is affected when the switching frequency is increased or decreased as a function of number of LC elements. Moreover, the converter was operated in non-inverting mode, the load was adjusted until  $V_{\text{out}}$  corresponded to 50% of  $V_{\text{in}}$  at 50 % duty cycle. The efficiency was recorded, see Fig. 14.

It is concluded that the efficiency increases with an increase in LC elements, but it also contains two local minimums at 40 and 64 elements. According to the simulation the optimum amount of LC elements is at 56 or 72 for this specific switch ratio.

Fig. 14 Efficiency as a function of number of LC elements.

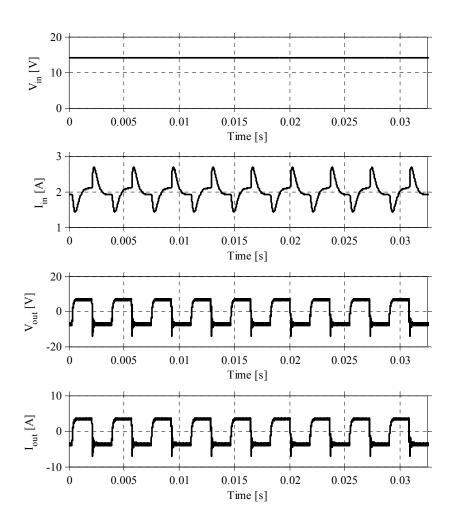

### 3.4 DC/AC Function

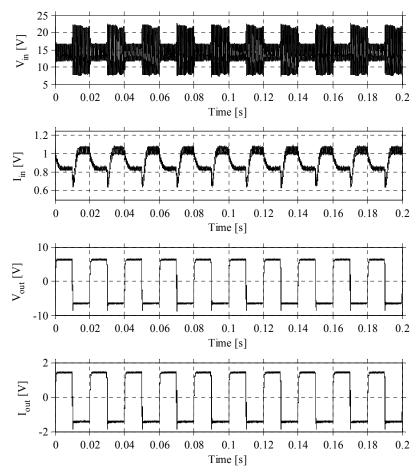

A low frequency modulation was applied to the gate voltage of switch  $S_{\rm C}$ . A transition from approximately negative (-7V) to positive (7V) output voltage, or vice versa, was effectuated every 1.8ms to create a 278Hz AC output voltage. To obtain an output voltage of  $\pm$ 7V, the load ( $R_{\rm load}$ ) was set to 2 $\Omega$  and the duty cycle was set to 25% for non-inverting mode and 35% for inverting mode.

The switch frequency for the switches  $S_A$ ,  $S_B$  (and  $S_C$  during non-inverted mode) was set to 84 kHz. Fig. 15 shows  $V_{in}$ ,  $I_{in}$ ,  $V_{out}$  and  $I_{out}$  during ten cycles. As seen, a DC/AC conversion is possible with the PBB converter. The efficiency was calculated according to

$$\eta = 100 \, \frac{P_{\text{out}}}{P_{\text{in}}} \tag{18}$$

where  $P_{out}$  and  $P_{in}$  is the average output and input power according to

$$P_{\rm out} = V_{\rm out} I_{\rm out} \tag{19}$$

$$P_{\rm in} = V_{\rm in} I_{\rm in} \,. \tag{20}$$

Furthermore, the converter efficiency was 82.5%.

Fig. 15 Input and output voltage & current to show the DC/AC function.

### **Chapter 4**

## 4 Mathematical Model

This chapter discusses the derivation of the transfer function and in detail how the transmission line theory can be applied to the converter in its non-inverting mode.

### 4.1 Transients in Non- inverting Operation

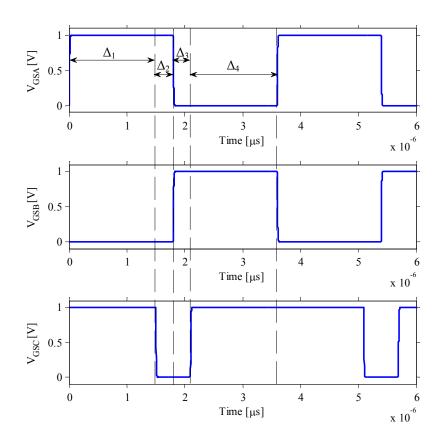

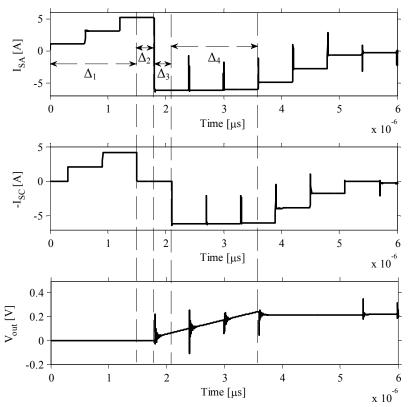

The same simulation setup as in section 3.2 were used, see Fig. 13. The duty cycle was set to 50% and the input voltage  $V_{in}$  to 14V. There are four different switch states forming a complete switch cycle, see Fig. 17.

Fig. 16 Switch patterns for  $S_A$ ,  $S_B$  and  $S_C$  during one and a half cycle at 50 % duty cycle.

These states corresponds to four time intervals designated  $\Delta t_1 - \Delta t_4$  and are calculated according to

$$\Delta t_1 = DT_s - t_d \tag{21}$$

$$\Delta t_2 = t_d \tag{22}$$

$$\Delta t_3 = t_d \tag{23}$$

$$\Delta t_4 = (1 - D)T_s - t_d \tag{24}$$

where D is the duty cycle,  $T_s$  the period time and  $t_d$  the time it takes for the wave to travel along the line from one end to the other.  $T_s$  and  $t_d$  [13] can be found as

$$T_{\rm s} = \frac{1}{f_{\rm sw}} \tag{25}$$

$$t_{\rm d} = N\sqrt{LC} \tag{26}$$

where  $f_{sw}$  is the switch frequency and N the number of LC elements in the LTL. It can be seen that switch  $S_A$  conducts during interval  $\Delta_1 - \Delta_2$ , switch  $S_B$  during interval  $\Delta_3 - \Delta_4$  and  $S_C$  during interval  $\Delta_1$  and  $\Delta_4$ .

The output voltage  $V_{out}$ , the input current  $I_{SA}$  at switch  $S_A$  and the output current  $-I_{SC}$  at switch  $S_C$  of the LTL are presented in Fig. 17. During interval  $\Delta_1$ , the input current increases step wise until interval  $\Delta_3$ . The same applies for the output current, except it increases until interval  $\Delta_2$  begin. During  $\Delta_2$ , all energy stored as a current wave is transformed into a voltage wave. When interval  $\Delta_3$  begins, all energy stored as a voltage wave is transformed back to a current wave. During interval  $\Delta_3 - \Delta_4$  the current charges the capacitor and the output voltage increases. This coincides well with the theoretical explanation made in section 2.5.

Fig. 17 Input and output current of the LTL and  $V_{out}$  during roughly one and half cycle at 50 % duty cycle.

#### 4.1.1 Interval $\Delta_1$

It has been stated that  $LTL_0$  is built with 40 LC elements of 100nH and 560pF. This gives a characteristic impedance of

$$Z_0 = \sqrt{\frac{L}{C}} \approx 13.4\Omega \,. \tag{27}$$

If the internal generator resistance  $Z_g$  is assumed to be zero and the input voltage  $V_{in}$  is set to 14V, the current wave magnitude can be calculated as

$$I_1^+ = \frac{V_{\rm in}}{Z_0 + Z_{\rm g}} \approx 1.047 \,\mathrm{A}$$

(28)

which initially propagates in the LTL. The magnitude is close to the simulated value of 1.045A, see  $I_{SA}$  at t<0.5µs in Fig. 17. The small difference is because of the inductance DC resistance in the input filter.

At the LTL end the load impedance  $Z_{L_2}$  is  $0\Omega$ , since  $S_C$  is conducting, see Fig. 18.

*Fig. 18* Circuit during interval  $\Delta_1$ , switch  $S_A$  and  $S_C$  conducting.

The reflection coefficient for each side of the LTL therefore becomes

$$\Gamma_{\rm L} = \frac{0 - Z_0}{0 + Z_0} = -1 \tag{29}$$

$$\Gamma_{\rm g} = \frac{0 - Z_0}{0 + Z_0} = -1 \tag{30}$$

where  $\Gamma_{\rm L}$  is the reflection coefficient at switch  $S_{\rm C}$  and  $\Gamma_{\rm g}$  the reflection coefficient at switch  $S_{\rm A}$ . The number of reflections at each end is

$$N_{\Gamma_{\rm L}} = \frac{DT_{\rm s} - t_{\rm d}}{2t_{\rm d}} = 2$$

(31)

$$N_{\Gamma_{\rm g}} = \frac{DT_{\rm s}}{2t_{\rm d}} = 3.$$

(32)

where  $N_{\Gamma L}$  is the number of reflections at  $S_C$  and  $N_{\Gamma G}$  is the number of reflections at  $S_A$ . Note that the last reflection at  $S_C$  does not increase the current amplitude in the case of 50% duty cycle. This is due to that  $S_A$  is turned off at the same instance as interval  $\Delta_1$  ends. The currents at each end become

$$I_{\rm SC} = I_1^{+} (1 - \Gamma_{\rm L} + \Gamma_{\rm L} \Gamma_{\rm g} - {\Gamma_{\rm L}}^2 \Gamma_{\rm g}) \approx 4.19 A$$

(33)

$$I_{\rm SA} = I_1^{+} (1 - \Gamma_{\rm L} + \Gamma_{\rm L} \Gamma_{\rm g} - \Gamma_{\rm L}^{2} \Gamma_{\rm g} + \Gamma_{\rm L}^{2} \Gamma_{\rm g}^{2}) \approx 5.24 \, A \, . \tag{34}$$

According to simulations, the currents become 4.15A and 5.18A. The small difference is because of DC resistance in the input and LTL inductances. In reality it would also involve crosstalk between the LC elements, but that is not included in the simulation.

#### 4.1.2 Interval $\Delta_2$

During this interval, switch  $S_A$  is still on and  $S_C$  is turned off, see Fig. 19.

*Fig. 19* Circuit during interval  $\Delta_2$ , switch  $S_A$  on and  $S_C$  off.

All energy stored as a current wave is transformed into a voltage wave according to

$$V^{-} = (N_{\Gamma_{\rm I}} + N_{\Gamma_{\rm c}})I_{1}^{+} + V_{\rm in} = 6V_{\rm in} = 84\,\rm V\,.$$

(35)

The voltage wave will begin to propagate towards switch  $S_A$ . It can be noticed that the current amplitude at switch  $S_A$  is constant for one  $t_d$  (half the time switch  $S_C$  is kept in off state). This means that the voltage wave will reach  $S_A$  when interval  $\Delta_3$  begins and it will not affect the current amplitude which was previously calculated to 5.24A. At switch  $S_{C_a}$  it can be seen that the current amplitude is zero because it is transformed into a voltage wave.

The reflection coefficient at  $S_A$  is the same as to  $\Gamma_g$  in (30) and at  $S_C$  it can be calculated as

$$\Gamma_{L1} = \frac{\infty - Z_0}{\infty + Z_0} = 1.$$

(36)

#### 4.1.3 Interval $\Delta_3$

The voltage wave front, created during interval  $\Delta_2$ , has reached switch  $S_A$  and  $S_B$  when interval  $\Delta_3$  begins. Switch  $S_A$  is turned off and Switch  $S_B$  are turned on, see Fig. 20.

All energy stored in the voltage wave in (35) is transformed into a current wave

$$I_{5}^{+} = -\frac{(N_{\Gamma_{L}} + N_{\Gamma_{g}})I_{1}^{+} + V_{in}}{Z_{0}} = -\frac{6V_{in}}{Z_{0}} \approx -6.29 \,\mathrm{A}$$

(37)

which propagates towards  $S_{\rm C}$ . It reaches the other end after one  $t_{\rm d}$ , the same time as interval  $\Delta_4$  begins. The simulated value of  $I_5^+$  is -6.2A and is still close to the

theoretical one. The difference is greater compared to the simulated value in interval  $\Delta_2$  because of the DC resistance losses in the LTL increases linearly dependent on the wave propagation time inside the LTL.

*Fig. 20* Circuit during interval  $\Delta_3$ , switch  $S_A$  off,  $S_B$  on and  $S_C$  off.

The load impedance is formed by the load ( $R_{load}$ ) parallel with the output capacitor ( $C_{out}$ ) according to

$$Z_{L2} = \frac{R_{\text{load}} X_{\text{C}}}{R_{\text{load}}^{2} + X_{\text{C}}^{2}} - j \frac{R_{\text{load}} X_{\text{C}}}{R_{\text{load}}^{2} + X_{\text{C}}^{2}}.$$

(38)

where  $X_c$  is the reactance. The reactance can be found as

$$X_{\rm C} = \frac{1}{2\pi f_{\rm sw} C_{\rm out}} \tag{39}$$

where  $f_{sw}$  is the switch frequency. In the simulation  $R_{load}$  was set to 5.9 $\Omega$ ,  $C_{out}$  to 50 $\mu$ F and the switching frequency to 277kHz. This result in a load impedance ( $Z_{L2}$ ) of 0-0.0113j $\Omega$  and a reflection coefficient as

$$\Gamma_{L_2} = \frac{|Z_{L2}| - Z_0}{|Z_{L2}| + Z_0} \approx -0.9983$$

(40)

The reflection coefficient at  $S_{\rm C}$  is the same as  $\Gamma_{\rm L1}$  in (36), i.e 1.

#### 4.1.4 Interval $\Delta_4$

The negative current wave, created during interval  $\Delta_3$ , has reached switch  $S_C$  when interval  $\Delta_4$  begins. Both  $S_B$  and  $S_C$  are on, see Fig. 21.

*Fig. 21* Circuit during interval  $\Delta_4$ , switch  $S_A$  off,  $S_B$  and  $S_C$  on.

The reflection coefficient at  $S_{\rm C}$  is the same according to  $\Gamma_{\rm L}$  in (29) and the reflection coefficient at the load impedance ( $C_{\rm out}$  parallel to  $R_{\rm load}$ ) is according to  $\Gamma_{\rm L2}$  in (40). The number of reflections at  $S_{\rm C}$  and at the load can be calculated as

$$N_{\Gamma_{\rm LI}} = \frac{DT_{\rm s} - t_{\rm d}}{2t_{\rm d}} = 2 \tag{41}$$

$$N_{\Gamma_{L_2}} = \frac{DT_s - 2t_d}{2t_d} = 2.$$

(42)

Since the reflection coefficient at the load is  $\Gamma_{L2}$ , the current at switch  $S_C$  increases by  $(1+\Gamma_{L2})$  every time the wave is reflected. Therefore the current barely increases during interval  $\Delta_4$ . Furthermore, it can be noticed in the simulation that all current will flow into the output capacitor. The current in a capacitor can be expressed as

$$i = C \frac{dv_{\rm c}}{dt} \tag{43}$$

which gives that

$$\Delta v_{\rm c} = \frac{I_{\rm L} \Delta t}{C} \tag{44}$$

where  $\Delta v_c$  is the voltage difference during the time the capacitor is charged by the current I<sub>L</sub>. The current I<sub>L</sub> can be assumed to be  $I_5^+$  since it barely changes during interval  $\Delta_3$  and  $\Delta_4$ . This gives a voltage difference according to

$$\Delta v_{\rm c} = \frac{I_5^{-}(\Delta t_3 + \Delta t_4)}{C} = 223 \, mV \,. \tag{45}$$

which is close to the simulated one of 217mV. This assumption can only be made during the first cycles and it was only made to verify that (43) is accurate compared to the simulation. At subsequent cycles, the current amplitude varies more during interval  $\Delta_3$  and  $\Delta_4$  because of reflections. The increase of  $v_c$  is therefore not linear during these intervals; it is rather equal to the increase in output voltage for each cycle. This is due to the fact that the capacitor is charged with energy during interval  $\Delta_3$  and  $\Delta_4$  every cycle. This results in an increased output voltage which eventually reaches a steady state DC value. The output voltage can be expressed as

$$V_{\rm out} = V + \Delta v_{\rm c} \tag{46}$$

where V is the output voltage from the previous cycle. If t = 0 and  $C_{out}$  is assumed to be completely discharged when starting the converter, V is initially zero.

The theoretical amplitude values of the current and voltage waves propagating in the LTL can be considered to be accurate compared to the simulation. As a result these mathematical models can be used to describe the currents and voltages propagating inside the LTL.

#### 4.2 Transfer Function

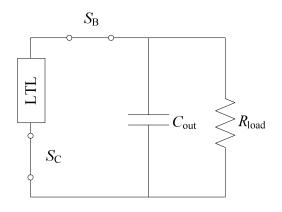

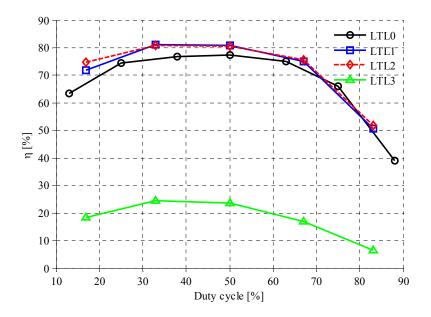

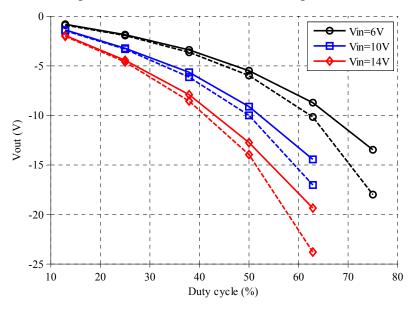

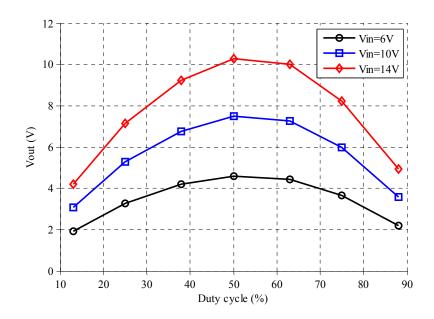

One of the goals was to investigate the transfer function of the PBB converter. Therefore, a simulation of  $V_{\text{out}}$  as a function of duty cycle was made. For the inverting mode, the simulated result can be seen in Fig. 22.

Fig. 22 V<sub>out</sub> as a function of duty cycle for 14V input voltage in inverted mode.

The solid line represents the simulated output voltage and the dashed an ideal Buck-Boost converter operating in continuous mode. As seen, the PBB converter in inverting mode works as a theoretical Buck-Boost converter. The transfer function can therefore be expressed as

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{-D}{1-D} \,. \tag{47}$$

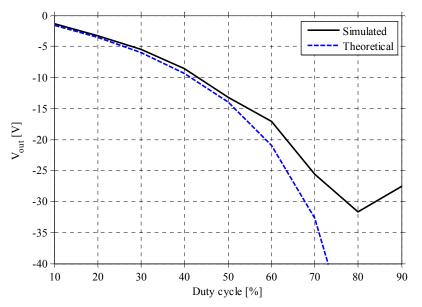

For the non-inverting mode the result is different compared to the inverting mode, see Fig. 23. As seen, the output voltage increases until 50% duty cycle and decline as the duty-cycle is further increased. None of the regular power electronic converters have this kind of transfer function.

Fig. 23 V<sub>out</sub> as a function of duty cycle for 14V input voltage in non- inverting mode.

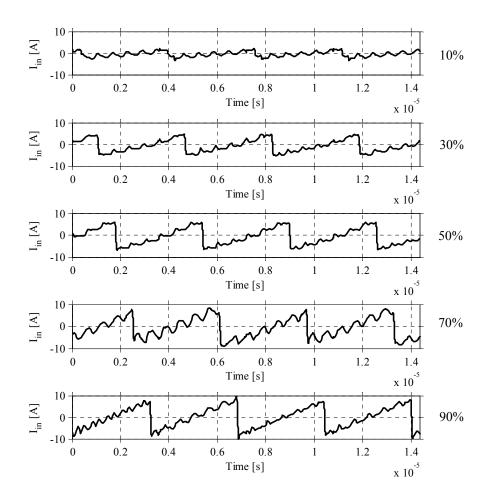

If the steady state current in the LTL is studied when operating in non-inverting mode, it can be seen that the average is approximately zero for all duty cycles, see Fig. 24. During the time intervals  $\Delta_1$ - $\Delta_2$  (the same time intervals as in section 4.1), the current increases almost linearly. When interval  $\Delta_3$  begins ( $S_A$  turns off,  $S_B$  turns on and  $S_C$  is kept in off state), the current polarity is changed to negative and start to increase almost linearly until next operation cycle were interval  $\Delta_3$  begin again. It can also be noted that the starting current ( $S_A$  turn on) and the maximum and minimum value of the current increases with duty cycle, see Table 1.

|   | Table 5 Steady state current data at different duty cycles D. |           |         |         |          |           |  |  |  |  |  |

|---|---------------------------------------------------------------|-----------|---------|---------|----------|-----------|--|--|--|--|--|

|   | D [%]                                                         | start [A] | min [A] | max [A] | diff [A] | Mean [mA] |  |  |  |  |  |

|   | 10                                                            | 1.3       | -3.7    | 2.8     | 6.5      | -388      |  |  |  |  |  |

|   | 30                                                            | 1.8       | -6.3    | 5.9     | 12.2     | -451      |  |  |  |  |  |

|   | 50                                                            | 0.0       | -8.3    | 7.1     | 15.4     | -194      |  |  |  |  |  |

|   | 70                                                            | -5.5      | -9.0    | 7.2     | 16.2     | -356      |  |  |  |  |  |

| I | 90                                                            | -6.8      | -9.0    | 8.4     | 17.4     | -151      |  |  |  |  |  |

Table 3 Steady state current data at different duty cycles *D*.

Two common techniques to derive the transfer function of a DC/DC converter, is Fourier analysis or state space averaging (SSA) [12]. In the Fourier analysis

method the DC component of a waveform is given by its average value. For example, in a Buck converter the transfer function is derived from the average voltage over the inductor. This can't be made with the PBB converter due to that the voltage across the LTL is varying with time and is depending on the reflection coefficients and the delay. Furthermore, in the SSA method, a Buck converter is modeled with Kirchoff's laws in its two circuit states, i.e when the switch is on and off. The equations are then converted into state space matrices and are averaged. This method can't be used straight away either, since the PBB converter has a transmission line instead of an inductor. Moreover, it was shown that the steady state current in the PBB converter almost increases linearly. By studying the slope in Fig. 24, it almost corresponds to an inductor with the same value as the total inductance of 40 L elements in the LTL, i.e 4µH. It could therefore be assumed that the LTL can be modeled as an inductor. However, there are still problems to use the state space averaging method. The first problem is that the inductor will be floating during interval  $\Delta_2$ - $\Delta_3$ . The second is that the current changes polarity when switch  $S_A$ turn off and S<sub>B</sub> turn on. Due to these problems the transfer function was not derived. Further work has to be made.

Fig. 24 The simulated steady state current into the LTL with different duty cycles to the right.

### Chapter 5

# 5 Inductance Design and Measurement

One of the goals was to obtain the same impedance for the new LTLs as the old one in order to be able to compare them regarding efficiency. This chapter explains the procedure to measure the inductance for the Coilcraft, U-cores and toroidal inductors. It also contains the measurement result and an analysis of the result.

#### 5.1 Equipment

The test equipment used for the following measurements is listed in Table 4.

| Table 4 Test equipment.      |

|------------------------------|

| Equipment                    |

| Inductance Analyzer (IA)     |

| Wayne Kerr precision IA 3245 |

| Wayne Kerr precision IA 3245 |

#### 5.2 Measurements

In all measurements the temperature was  $\sim 25^{\circ}$ C. The inductance analyzer was set to 300kHz and 25mA AC.

#### 5.2.1 Coilcraft Inductance

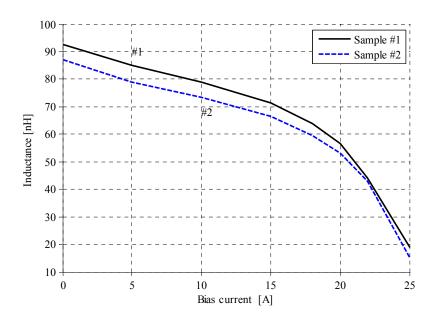

The inductor analyzer was used to measure two Coilcraft SLC7530S-101MLC inductances to verify if they correspond to the datasheet. Two short 1mm wires were soldered on each side of the inductors and connected to the crocodile clamps of the analyzer. The result of the two samples can be seen in Fig. 25. The inductance is within the tolerance of  $100nH\pm20\%$  for bias currents less than 5A. Furthermore, these measurements are hard to compare to the datasheet due to the manufacturers deficient descriptions of measurement setup. Therefore, this measurement should only be used for comparison for the U-cores.

Fig. 25 Inductance as a function of bias current for to Coilcraft inductor samples.

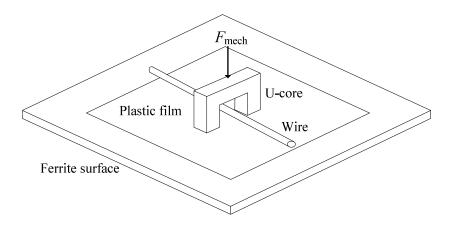

#### 5.2.2 U-core Air Gap Adjustment

The inductor design of LTL<sub>1</sub> and LTL<sub>2</sub>, was made by placing the U-core on top of a ferrite plate. This quadratic plate designated TKD-EPC QU40/40/2, was 2mm thick and 40x40mm wide. In order to achieve an inductance of roughly 100nH, an air gap was required between the U-core and the ferrite plate. To achieve an air gap, different plastic films were evaluated. They were placed between the Ferrite plate surface and the U-core. Moreover, a 1mm thick wire were routed between the U-core legs and connected to the analyzer, see Fig. 26. Furthermore, an undefined mechanical force  $F_{mech}$  was applied on top of the U-cores in order to obtain accurate inductance result.

Fig. 26 Measurement setup illustrating the Ferrite surface, plastic film, U-core and wire.

The measured inductance for five U-core samples with different plastic films can be found in Table 5. Since the values should be as close as possible to 100nH, it

can be noticed that one layer of 0.0254 mm plastic film gives the best result. It was also observed that the ferrite surface affected the inductance value by 8.5-10nH depending on position during the measurement. The minor impact was neglected.

| Plastic film<br>Thickness [mm] |         |         | Sample #003<br>[nH] | Sample #004<br>[nH] | Sample #004<br>[nH] |

|--------------------------------|---------|---------|---------------------|---------------------|---------------------|

| _                              | 186-202 | 230-246 | 152-174             | 187-206             | 215-200             |

| 0.0254                         | 88.5    | 94.0    | 91.5                | 93.0                | 92.0                |

| 0.0508                         | 58.0    | 61.0    | 60.0                | 60.0                | 60.0                |

| 0.0762                         | 41.0    | 43.0    | 42,5                | 42,5                | 41.0                |

| 1.7780                         | 39,5    | 30.0    | 30.0                | 32.0                | 31.0                |

Table 5 The U-core inductance with different plastic films for five samples.

#### 5.2.3 Ferrite U-core Inductance

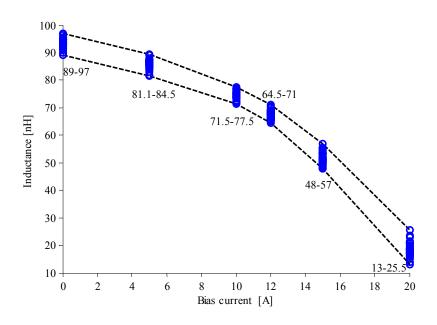

Different DC bias currents were applied to 80 U-core samples with a 0.0254mm thick plastic film between the U-core and ferrite surface. The force applied on top of the U-core was measured with a precision scale and varied between 7.76-7.95Nm. The small variation in force was observed to not affect the measured inductance, due to the inductor analyzer accuracy of 0.5nH. However, during measurement, it was noted that the inductance value varied depending on the analyzer temperature and wire and ferrite surface position. With all these factors taken into account, the measurement uncertainty was estimated to be  $\pm 4$ nH. The inductor analyzer was therefore calibrated before and after each U-core measurement.

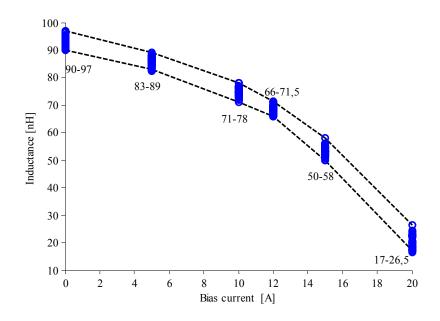

The result for the 40 U-cores used in  $LTL_1$  and  $LTL_2$  can be seen in Fig. 27 and Fig. 28. The circles, shown as vertical thick lines, represent the measured values at different bias currents. The dotted lines show the interval between the lowest and highest values and the numbers point out the minimum and maximum value of each measuring node. It can also be seen, that the inductance value is slightly lower than the two Coilcraft samples in section 5.2.1 up to 10A. At 10A bias current the inductance value for the U-cores and Coilcraft inductances deviate roughly 20% from the inductance value at zero bias current. This is considered acceptable.

In section 4.2, it was shown in a simulation that the highest current magnitude in steady state would be 9A at 90 % duty cycle. However, as mentioned in 3.2, it is not reasonable to operate the PBB converter at really low or high duty cycle, due to the decrease in efficiency. Therefore, the current of 8.3A at 50% duty cycle is considered to be the maximum current for the design of inductor cores. Since it is lower than 10A and has a decent safety margin of roughly 17%, the U-cores was accepted for use in the PBB converter.

Fig. 27 Inductance as a function of bias current for the 40 U-cores used in LTL<sub>1</sub>.

Fig. 28 Inductance as a function of bias current for the 40 U-cores used in LTL<sub>2</sub>.

#### 5.2.4 Ferrite Toroidal Core Inductance

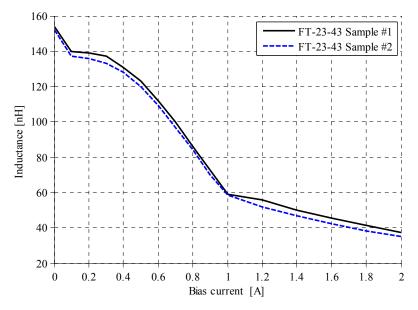

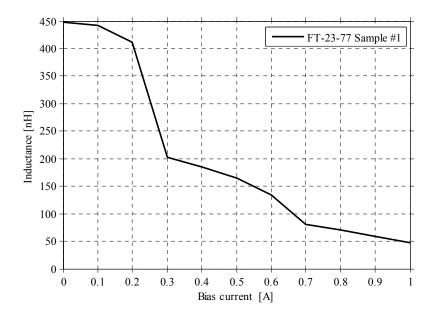

To verify that the toroidal core for  $LTL_3$  has acceptable inductance when bias current is applied, the inductance of one sample of Amidon FT-23-77 and two samples of Amidon FT-23-43 toroidal cores were measured. As seen in Fig. 29, the two samples of FT-32-43 are far away from 100nH and saturates at less than 1A. It is much lower than the simulated current of 8.3A at 50% duty cycle. Therefore, these toroids will be saturated and if used in the PBB converter, the efficiency will be reduced compared to the U-cores. The result of the FT-32-77 sample is shown in Fig.

30. It can be seen that the inductance varies too much and as a result was excluded for further use in the converter.

Fig. 29 Inductance as a function of bias current for two samples of the toroid FT-23-43.

Fig. 30 Inductance as a function of bias current for one sample of the toroid FT-23-77.

### **Chapter 6**

# **6** LTL Impedance Measurement

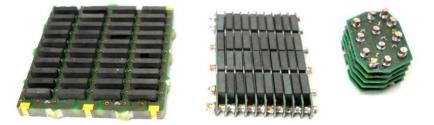

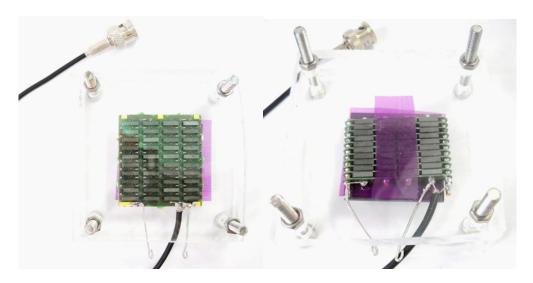

It was shown in the previous chapter that the inductance value for the U-cores was close to the Coilcraft inductances up to 10A and the toroids between 0.4-0.7A. This doesn't necessarily mean they have the same total impedance as  $LTL_0$  if they are put inside  $LTL_{1-3}$ . In order to be able to compare if the impedance of  $LTL_{1-3}$  is close to the  $LTL_0$ , the LTLs were assembled and the impedance as a function of frequency was measured. The assembled LTLs can be seen in Fig. 31.

Fig. 31 The different LTLs; from left LTL<sub>1</sub>, LTL<sub>2</sub> and LTL<sub>3</sub>.

#### 6.1 Equipment

The measurement equipment used for the impedance measurement is listed in Table 6.

| Equipment                     |

|-------------------------------|

| Vector Network Analyzer       |

| Rohde & Schwarz ZVC           |

| Impedance/Gain-phase Analyzer |

| HP4194A                       |

| HP16034B test tweezers        |

Table 6 Test equipment for impedance measurement.

#### 6.2 Measurement Setup

The input impedance was measured in two ways. The first way was to measure the input reflections (complex  $\Gamma$ ) by sinusoidal waves with different frequencies and derive the impedance from

$$Z_{\rm in} = Z_0 \frac{1+\Gamma}{1-\Gamma} \tag{48}$$

where  $\Gamma$  is the reflection coefficient and  $Z_0$  is the characteristic impedance [13]. A vector network analyzer Rohde & Schwarz ZVC was used. The other way was to measure the absolute input impedance  $|Z_{in}|$  with an impedance analyzer HP4194A.

For the reflection measurement method, the output power of the sinusoidal wave was set to -10dBm, the start frequency to the lowest possible i.e (20kHz) and the end frequency to 5MHz. Coaxial cables were soldered to the input and the output were short circuit to ground with a 1mm thick wire for each LTL. The instrument was calibrated with each coaxial cable for short circuit, open circuit and with a matched resistor of 50 $\Omega$  before the cables were soldered on the LTLs.

To obtain the characteristic impedance, the values for the Coilcraft inductor and Murata capacitor were used in (48), i.e L was set to 100nH, C to 560pF and the resistance to  $0.123m\Omega$  which is the DC resistance value of the inductor. G was set to zero due to the problem of approximating the conductance of a surface mounted inductor and capacitor. The ESR value of the capacitance was neglected due to its minor impact on R. It can also be noted that the characteristic impedance depends on the frequency. However, this was neglected, since the impact is considered to be insignificant.

For the impedance measurement, the start frequency was set to the lowest possible (i.e 100Hz) and the end frequency to 5MHz. To measure the input impedance, HP16034B test tweezers were used on the input and output of the LTL. The instrument was calibrated with the tweezers for short circuit, open circuit and with a matched resistor of  $50\Omega$ .

An acrylic glass device was used to keep constant and even pressure on the Ucores in  $LTL_1$  and  $LTL_2$ . In addition for  $LTL_2$ , the center U-cores were loose, due to height tolerances. Hence, a strip of the same plastic film as between the Ferrite surface and U-core was used in order to apply more even pressure on the U-cores. Furthermore, two 1mm thick wires were soldered on the input and output for the impedance measurement, see Fig. 32 and 33 for LTLs with additional connections. For complete LTL specifications, see appendix D.

*Fig. 32* Two acrylic plates tighten under and above LTL<sub>1</sub> and LTL<sub>2</sub>. A strip of purple film was used on the center lines of U-cores to apply even pressure.

Fig. 33 A coaxial cable and 1mm wire soldered on LTL<sub>3</sub>.

#### 6.3 Measurements

The first conclusion from the measurement is that the input impedance varied depending on the type of measurement instrument. It can be seen in Fig. 34 that the input impedance measured with Rohde & Schwarz network analyzer has an offset of roughly 8dB compared to the same measurement with the HP4194 impedance analyzer. The same behavior was recorded for all four LTLs and it is believed to origin from a vaguely described offset in the operation manual. The manual mentions that there could be an offset varying between 0-9dB without further explanations. Consequently, that is why two instruments were used to validate the result.

It can also be seen in Fig. 34 that  $LTL_0$  almost had the same resonance frequency as the theoretical curve. This is most likely because all 40 Coilcraft inductances had the average value close to 100nH. It can also be noted that the two Coilcraft inductor samples measured in section 5.2.1, had less than 100nH, but it is known from Table 1 that they have a  $\pm 20\%$  tolerance. The capacitors have a tolerance of  $\pm 5pF$  which do not affect the resonance frequency in a distinguishable way.

*Fig. 34* The theoretical and measured input impedance independent of characteristic impedance for LTL<sub>0</sub>. The instrument used for this measurement is Rohde & Schwarz vector analyzer and HP4194A impedance analyzer.

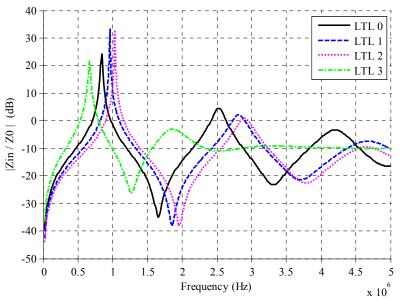

The measured impedance for  $LTL_1$  and  $LTL_2$  shows that they have a slightly higher resonance frequency than  $LTL_0$ , see Fig. 35. This is reasonable since all the measured U-cores in section 5.2.3 had an inductance lower than 100nH at zero bias current. It can also be seen that  $LTL_3$  has the lowest resonance frequency. This is also reasonable, since the toroid samples in section 5.2.4 were measured to have an inductance of roughly 50nH higher than 100nH. Furthermore, the total DC resistance value for  $LTL_{1-3}$  was several times lower then for  $LTL_0$ , see Table 7.

*Fig.* 35 The input impedance independent of characteristic impedance on all LTLs measured with HP4194A impedance analyzer.

| LTL | DCR $[m\Omega]$ |

|-----|-----------------|

| 0   | 18.6            |

| 1   | 5.96            |

| 2   | 1.55            |

| 3   | 3.06            |

| Table 7 Total DC resistance for each LTL. |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

### **Chapter 7**

## 7 Efficiency Optimization

In the previous chapter, the LTLs were compared to each other with respect to impedance as a function of frequency. This chapter analyzes the optimum efficiency of the PBB converter with the different LTLs. The optimization is done in non-inverting mode.

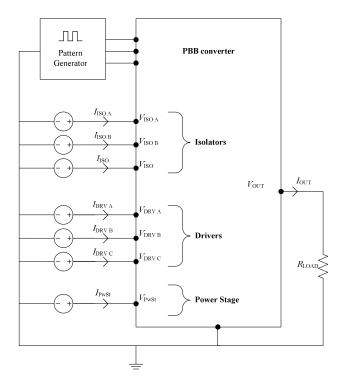

#### 7.1 Measurement Setup

To control the MOSFETS and not have the same ground potential for all switches (Source on  $S_A$  and  $S_B$  is not connected to ground), digital isolators and drive circuits is used in the PBB converter. Four power supplies were used to supply the isolators, drivers and the power stage of the converter. The isolator voltages were set to 3.3V, the driver voltages to 5.5V and the input voltage was set to maximum 14V. The input, output and driver voltages and currents were measured using both true RMS multimeters and oscilloscope probes. The gate patterns were created using an Agilent 16903A logic analysis system, see Fig. 36 for measurement setup.

Fig. 36 Measurement setup for efficiency measurement with the different LTLs.

When  $LTL_{1-3}$  was connected to the converter, the first and last L element of  $LTL_0$  was removed from the converter. Two 2mm thick copper wire were then soldered between the original input and output of  $LTL_0$  to the input and output of the LTL, see Fig. 37. The LTL was also connected to the same ground plane as the rest of the converter via a ground wire.

*Fig. 37* Prime Buck-Boost converter with LTL<sub>1</sub> connected.

For the following measurements the input power can be found as

$$P_{\rm in} = P_{\rm drv} + P_{\rm PwSt} + P_{\rm iso} \tag{49}$$

where  $P_{drv}$  is the driver power,  $P_{PwSt}$  the PowerStage input power and  $P_{iso}$  the isolator power. The isolator power is low (<2mW) and fairly constant. Thus, it was considered negligible and not recorded.  $P_{drv}$  and  $P_{PwSt}$  can be calculated as

$$P_{\rm drv} = \left(V_{\rm drvA} I_{\rm drvA}\right) \left(V_{\rm drvB} I_{\rm drvB}\right) \left(V_{\rm drvC} I_{\rm drvC}\right)$$

(50)

$$P_{\rm PwSt} = V_{\rm PwSt} I_{\rm PwSt} .$$

<sup>(51)</sup>

The output power is defined as

$$P_{\rm out} = V_{\rm out} \,\mathrm{I}_{\rm out} \tag{52}$$

and the efficiency and powerstage efficiency can be calculated as

$$\eta = 100 \, \frac{P_{\text{out}}}{P_{\text{in}}} \tag{53}$$

$$\eta_{\rm PwSt} = 100 \, \frac{P_{\rm out}}{P_{\rm PwSt}} \tag{54}$$

#### 7.1.1 Equipment

The test equipment can be found in Table 8. Some components were removed and changed on the prototype converter before the efficiency was measured, see Appendix C.

| Table 8 Test equipment for the following measurement | ts. |

|------------------------------------------------------|-----|

| Equipment                                            |     |

| Logic analysis system and equipment                  |     |

| Agilent 16903A                                       |     |

| Agilent 16720A Pattern Generator (module)            |     |

| Agilent 16522-61601 Output Cable                     |     |

| Agilend 10566A 3-state TTL / 3.3 Data Pod            |     |

| Power Supplies                                       |     |

| TTi EX354D                                           |     |

| Powerbox 3000 B                                      |     |

| Powerbox 3000 B                                      |     |

| Delta Elektronika SM 7020-D                          |     |

| Multimeter (True RMS Multimeter)                     |     |

| Fluke 87                                             |     |

| Tektronix TX3                                        |     |

| Oscilloscope and probe                               |     |

| LeCroy WaveSurfer 44MXsB 400 MHz                     |     |

| LeCroy PP005A 500Mhz Probe                           |     |

| LeCroy PP006A 500 Mhz Probe                          |     |

| LeCroy AP015                                         |     |

| IR Camera                                            |     |

| Flir ThermaCam 300                                   |     |

| Adjustable load                                      |     |

| Metrel 100Ω 1,8A                                     |     |

| Berco 5Ω                                             |     |

Table 8 Test equipment for the following measurements.

#### 7.2 Measurements

The efficiency optimization was done in the following procedure:

- 1. Measurement of LTL delay time.

- 2. Switch frequency and switch  $S_{\rm C}$  off time adjustment.

- 3. Introduction of dead time between  $S_A$  and  $S_B$ .

- 4. Adjustment of the load until  $V_{out}$  correspond to 50 % of  $V_{in}$ .

- 5. Recording of efficiency with RMS multimeters and oscilloscope probes.

#### 7.2.1 LTL delay time

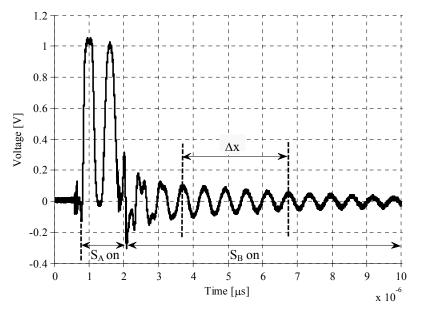

The delay time, i.e. the time it takes for the voltage wave to travel back and forth along the LTL, was measured by applying a short voltage pulse into the LTL. This was achieved by turning on switch  $S_A$  for a short period, turn it off and let switch  $S_B$ conduct for a long time. By doing this, the reflections in the voltage wave could be measured over time, see Fig. 38.

Fig. 38 Reflections along LTL<sub>0</sub> when applying a short pulse.

The delay time can be found with

$$T_{\rm s} = \frac{\Delta x}{M} \tag{55}$$

where  $\Delta x$  is the time interval between the reflections and M is the number of reflections. In order to obtain an accurate result, the mean time value was calculated for five reflections. The result for the different LTLs can be found in Table 9.

| Table 9 Delay time | in the different LTLs. |

|--------------------|------------------------|

| LTL                | Delay [ns]             |

| 0                  | 606.2                  |

| 1                  | 549                    |

| 2                  | 535.8                  |

| 3                  | 783.4                  |

1.00

The theoretical delay time with an inductance of 100nH and a capacitance of 560pF can be calculated as

$$T_{\rm s} = 2t_{\rm d} = 2N\sqrt{LC} = 2\cdot40\cdot\sqrt{100\cdot10^{-9}\cdot560\cdot10^{-12}} = 599ns\,.$$

(56)

The delay time of  $LTL_0$  is close to the theoretical one; meanwhile  $LTL_{1-2}$  has a slightly shorter delay time and  $LTL_3$  a longer delay. This seems reasonable compared to the impedance measurements in section 6.3, since the first resonance frequency is lower for  $LTL_3$  and higher for  $LTL_{1-2}$ , compared to  $LTL_0$ .

#### 7.2.2 Switch Frequency

The switch frequency plays a big role in how high the efficiency becomes. A simplified explanation is that if the switch frequency is high, the switching losses in the MOSFET increase. It also results in a higher power demand for the MOSFET drivers and as a consequence lowers the efficiency. On the other hand, if the switch frequency is too low, the imaginary part of the converter inductive impedance

$$Z_{\rm ind} = DCR + j\omega L \tag{57}$$

decreases and the DC resistance becomes more distinct. Hence, the losses increase.

The clock period of the pattern generator was put to a  $100^{\text{th}}$  of the delay time. This means that  $2t_d$  equals 100 segments. This was made because of the pattern generator had a limiting clock frequency between 1MHz and 300MHz. It was also a way to easily decrease the switch frequency by adding 100 segments each time. Consequently, the switch frequency is adjusted as an integer of  $2t_d$  and could not be set to arbitrary values. This had to be accepted since no other options were available.

#### 7.2.3 Input Voltage

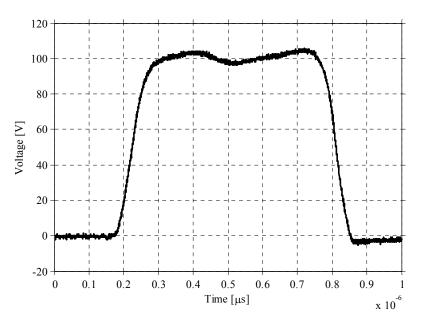

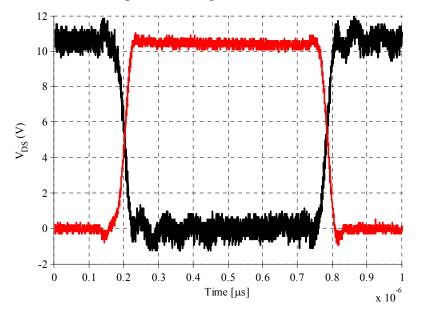

It was seen that the efficiency increased when the input voltage increased. A limiting factor of the input voltage was the LTL capacitor voltage at switch  $S_{\rm C}$  (LTL output end). According to the capacitor datasheet, it has a maximum recommended voltage of 50V. However, if an input voltage of 14V with 50% duty cycle were used, it resulted in a voltage wave with a magnitude of 102V in LTL<sub>0</sub>, see Fig. 39. Therefore, no further increase on input voltage was made. The voltage wave amplitude for the other LTLs was roughly the same.

Fig. 39 Maximum voltage wave amplitude at switch S<sub>C</sub> for LTL<sub>0</sub>.

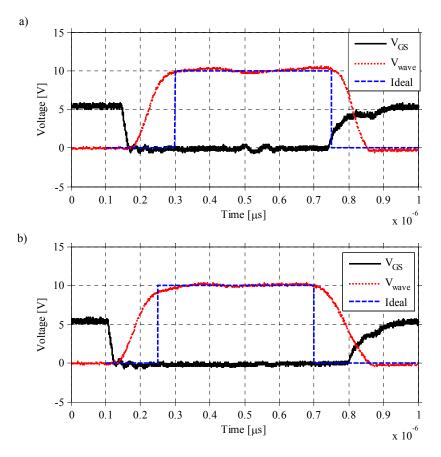

#### 7.2.4 Switch *S*<sub>C</sub> Off Time

The time it takes for the voltage and current waves to propagate back and forth along the LTL, has been mentioned to be  $2t_d$ . Switch  $S_C$  must therefore be turned off  $2t_d$  to completely inverse the voltage wave polarity. In reality the wave is no ideal square pulse and has a certain fall and rise time. It is also partially outspread over a slightly longer time interval because of dispersion. Consequently, some parts of the wave will not be inverted if the off time is exactly  $2t_d$ . The non-inverted wave will add up to the inverted wave and result in a decrease in efficiency, see Fig. 40a. The black line represent  $V_{GS}$  in switch  $S_C$ , the blue dashed line the ideal wave and the dotted red one the real voltage wave divided by 10 at  $S_C$ . As seen a part of the tail is not included during the off time of switch  $S_C$  off time. It can be seen that the tail is more included which result in less losses and higher efficiency. The efficiency as a function of switch  $S_C$  off time can be found in Fig. 41. An increase of the off time above 100 segments ( $2t_d$ ) increase the efficiency for each LTL.

*Fig. 40* Different off times on switch  $S_{\rm C}$ . a) has Mcoff 100 b) has Mcoff 116.

Fig. 41 Number of S<sub>C</sub> switch off segments as a function of efficiency. a) LTL<sub>0-2</sub> b) LTL<sub>3</sub>.

#### 7.2.5 Dead Time for Switch $S_A$ and $S_B$

To avoid cross conduction losses, dead time is normally introduced in power electronic converters. The purpose is to avoid the high side switch to conduct at the same time as the low side switch, or vice verse. This is done by adding a delay time, according to the fall time of the  $V_{\text{DS}}$  voltage for both switches.

Introducing dead time to switch  $S_A$  and  $S_B$  surprisingly decreased the efficiency for each LTL. The cause is believed to be that the increased energy accumulation, due to the longer conduction time of switch  $S_A$ , is higher than the cross conduction losses. Therefore, no dead time were introduced, see Fig. 42. It can be seen that  $S_A$ and  $S_B$  in LTL<sub>0</sub> are on a short interval at the same time. The duty cycle was set to 50% and  $S_C$  off time to 116 segments during this measurement.

Fig. 42 Switch S<sub>A</sub> and S<sub>B</sub> going from ON to OFF and vice verse for LTL<sub>0</sub>.