### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### **Single Phase Active Power Factor Correction Converters**

Methods for Optimizing EMI, Performance and Costs

### **SUPRATIM BASU**

Department of Energy and Environment Division of Electric Power Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden, June 2006.

### **Single Phase Active Power Factor Correction Converters**

Methods for Optimizing EMI, Performance and Costs SUPRATIM BASU ISBN 91-7291-770-9

© SUPRATIM BASU, 2006

Doktorsavhandling vid Chalmers Tekniska Högskola Ny serie nr. 2452 ISSN 0346-718X

Department of Energy and Environment Division of Electric Power Engineering Chalmers University Of Technology SE-412 96 Göteborg Sweden Telephone +46 (0)31-772 1000

Chalmers Bibliotek, Reproservice Göteborg, Sweden, 2006

# **Single Phase Active Power Factor Correction Converters**Methods for Optimizing EMI, Performance and Costs

**SUPRATIM BASU**

Department of Energy and Environment Division of Electric Power Engineering Chalmers University Of Technology

### **Abstract**

In this thesis, front-end solutions with single-phase power factor correction (PFC) capability are studied. The reduction of current harmonics using various PFC techniques is investigated and related to the EN 61000-3-2 standard. Moreover, power electronics issues concerning diode recovery characteristics, boost inductor design and MOSFET switching speed considerations for optimizing the overall EMI and efficiency performance of continuous mode active PFC Converters are studied. In addition, the design and construction of a 1200 W continuous conduction mode (CCM) PFC circuit prototype, used for making various measurements, is presented and discussed.

With the main objective of this dissertation being optimizing performance and cost indices of continuous mode PFC converters, the results of this research work are presented in three main parts.

Firstly issues related to generation of harmonic currents by AC-DC single-phase rectifier-capacitor filter circuits when connected to the utility network, the legal obligations set forth by the European standard EN 61000-3-2 for limiting generation of low-frequency harmonics and different PFC techniques and strategies useful for meeting this standard, are studied. A novel approach of having a central PFC circuit for domestic and commercial loads leading to lower current harmonic distortion without the need to install (expensive) active rectifiers in each end-user device is proposed.

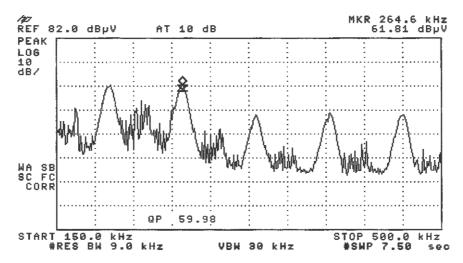

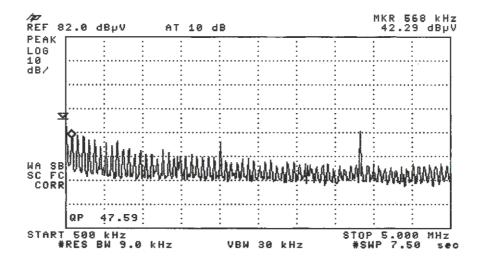

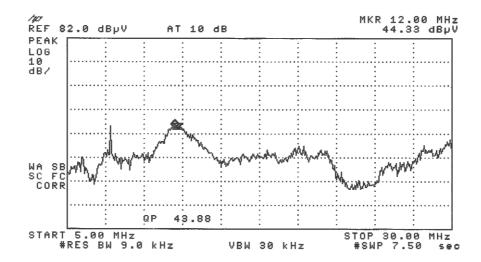

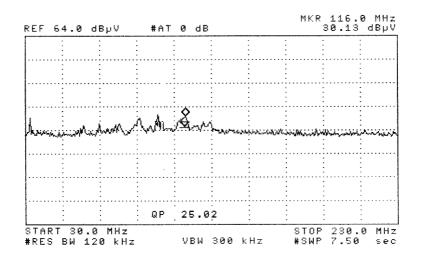

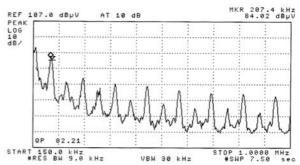

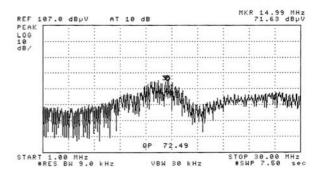

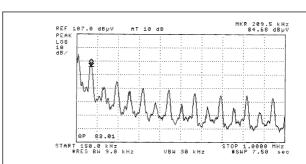

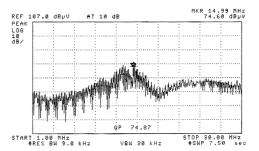

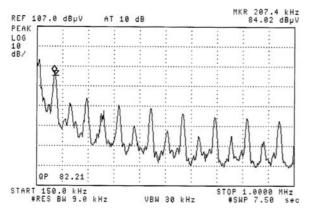

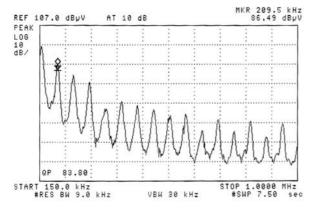

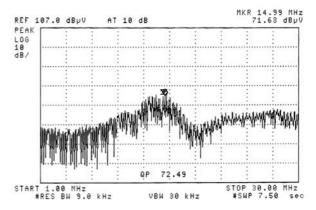

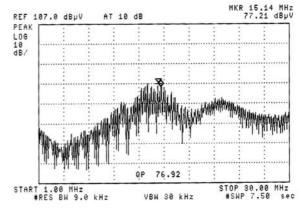

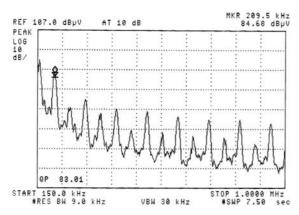

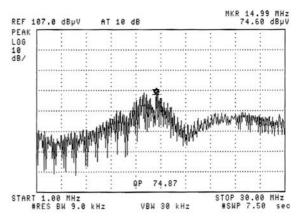

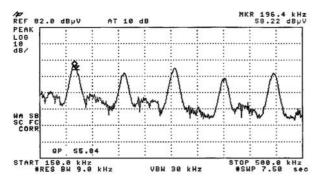

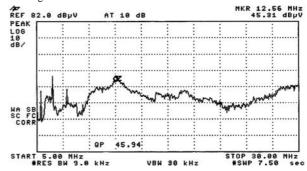

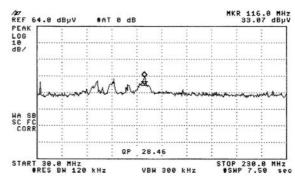

Secondly, based on various measurement results, some new methods to optimize overall EMI and efficiency performance of continuous mode active PFC circuits are presented. These methods resulted in performance improvements by way of higher efficiency, cost reduction and reduction in radiated and conducted EMI by over 10 to 23 dB  $\mu$ V.

Lastly, all papers published in various journals and conferences from the above work, are presented.

**Keywords:** Active and Passive Power Factor Correction (PFC), Harmonic Currents, Diode Recovery Time, Snap Factor, EMI, Quasi Peak, Antenna Factor.

### **List of Publications**

This thesis is based on the work contained in the following publications:

### Paper A

Supratim Basu, Math H.J.Bollen and Tore M.Undeland, *PFC Strategies in light of EN 61000-3-2*, **EPE PEMC 2004 Conference**, Riga, Latvia, 1-3 September 2004.

### Paper B

Supratim Basu and Math.H.J.Bollen, *A Novel Common Power Factor Correction Scheme for Homes and Offices*, **IEEE Transactions on Power Delivery**, Vol.20, No.3, July 2005.

### Paper C

Supratim Basu and Tore M.Undeland, *Design Considerations for Optimizing Performance & Cost of Continuous Mode Boost PFC Converters, IEEE Nordic Workshop on Power and Industrial Electronics (NORPIE 2004),* Trondheim, Norway, 14-16 June 2004.

### Paper D

Supratim Basu and Tore M.Undeland, *Diode Recovery Characteristics Considerations for Optimizing Performance & Cost of Continuous Mode Boost PFC Converters*, **EPE Journal**, Vol. 16. n° 1, February 2006.

### Paper E

Supratim Basu and Tore M.Undeland, *Inductor Design Considerations for Optimizing Performance & Cost of Continuous Mode Boost PFC Converters*, 20<sup>th</sup> Annual **IEEE Conference**, **APEC 2005** at Texas, USA, 6-10 March 2005.

### Paper F

Supratim Basu and Tore M.Undeland, *Diode Recovery Characteristics Considerations for Optimizing EMI Performance of Continuous Mode Boost PFC Converters*, 11<sup>th</sup> European Conference on Power Electronics and Applications, EPE 2005, at Dresden, Germany, 11-14 September 2005.

#### Paper G

Supratim Basu and Tore M.Undeland, A Novel Design Scheme for Optimizing EMI and Efficiency of Continuous Mode PFC Converters, 17<sup>th</sup> IEEE International Symposium on Electromagnetic Compatibility, Singapore, February 27-March 3, 2006.

### Paper H

Supratim Basu and Tore M.Undeland, *A Novel EMI Reduction Design Scheme for Continuous Mode PFC Converters*, Accepted for Publication-IEEE Nordic Workshop on Power and Industrial Electronics (NORPIE 2006), Lund, Sweden, 12-14 June 2006.

### Paper I

Supratim Basu and Tore M.Undeland, A Novel Design Scheme for Optimizing Efficiency and EMI of Continuous Mode PFC Converters, Submitted to - IEEE Transactions on Electromagnetic Compatibility, February 2006.

### **Preface**

The effect of poor power factor and harmonics generated by rectifier-capacitor filter circuits, encountered commonly in the input circuit of most off-line converters of electronic equipment, has been a matter of concern for long. At higher power levels (200 W to 500 W and higher) these problems become even more severe and thus harmonics must be filtered. This has led to the development of the IEC 61000-3-2 standard and its adoption by the European Community.

To mitigate the problems described above, power factor correction (PFC) circuits are being increasingly used. These PFC circuits could be of active or passive types. The passive PFC circuit comprises of a distortion-limiting network that helps in meeting the standard without suppressing the harmonics completely or improving the converter's power factor to unity. The active PFC circuit is a high frequency converter that provides near unity load power factor, with the load generating negligible harmonics, and this is also consistent with the goals of switch mode conversion (small size and lightweight). With power supply applications demanding significantly increased power densities of above 18 W / cubic inch, an increase in switching frequency, reduction in switching losses and EMI are a necessity.

The work presented here proposes new application areas for PFC circuits with reference to the IEC 61000-3-2 standard. Associated power electronics issues are also explored and design considerations that help improve overall performance of active PFC circuits are proposed. No work was done on various control schemes of these converters.

The work involved in this thesis has been carried out at the Department of Electric Power Engineering of Chalmers University of Technology Sweden, the Department of Electric Power Engineering of Norwegian University of Science and Technology (NTNU) Norway, and Bose Research (P) Ltd. India.

## Acknowledgement

I would like to express my sincere appreciation to those who made this work possible: Professors, friends and family.

Firstly, I would like to express my gratitude and admiration for my advisors Professor Tore M. Undeland and Professor Math H. J. Bollen, whose valuable scientific guidance and encouraging attitude have motivated much of the research described in this dissertation. I consider myself fortunate to have worked under their guidance. I thank them for their support, belief, patience, fairness and constructive feedback. They taught me something beyond just techniques for solving problems. They taught me attitude, initiative, and passion for what I believe in. I have to thank them for the many opportunities they have given me over the years.

I also take this opportunity to thank my colleagues for the pleasant times at the department, and Associate Professor Torbjörn Thiringer for all his constructive views and discussions.

I would like to thank Professor Kankar Bhattacharya who initiated this research project and has supported my work during the years.

I would also like to thank my colleague Shibu K., without whom this thesis would not have been finished in the way it has.

I would like to express my greatest admiration for my parents who constantly motivated and encouraged me to keep working towards this goal. I also thank all my other family members for all the support given during difficult times. I thank my wife Debrupa for her "always available" support and help.

## **List of Acronyms**

AC: Alternating Current

CCM: Continuous Conduction Mode

CENELEC: European Committee for Electrotechnical Standardization

CISPR: International Committee for Radio Interference

CM: Common Mode

CRM: Critical Conduction Mode

DCM: Discontinuous Conduction Mode

DC: Direct Current

DM: Differential Mode

EMI: Electromagnetic Interference

IEC: International Electrotechnical Committee

LISN: Line Impedance Stabilization Network

LN: Line-to-neutral

MOSFET: Metal Oxide Semiconductor Field Effect Transistor

PFC: Power Factor Correction

PWM: Pulse Width Modulation

RMS: Root Mean Square

THD: Total Harmonic Distortion

ZVS: Zero-Voltage Switching

# **Contents**

| Al | bstract                                                                                                                                                                                                                                                                                                                                  | iii                                                                       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Li | st of Publications                                                                                                                                                                                                                                                                                                                       | V                                                                         |

| Pr | reface                                                                                                                                                                                                                                                                                                                                   | vii                                                                       |

| A  | cknowledgement                                                                                                                                                                                                                                                                                                                           | ix                                                                        |

| Li | ist of Acronyms                                                                                                                                                                                                                                                                                                                          | xi                                                                        |

| Co | ontents                                                                                                                                                                                                                                                                                                                                  | xiii                                                                      |

| 1. | Introduction 1.1 Problem Overview and Research Goals 1.2 Previous Work                                                                                                                                                                                                                                                                   |                                                                           |

| 2. | Aim of the Work and Contribution 2.1 Specific Problem Areas and Publications                                                                                                                                                                                                                                                             | <b>5</b><br>5                                                             |

| 3. | Need for Power Factor Correction and Solutions 3.1 Definitions 3.2 Need for Power Factor Correction 3.3 Requirements as Per Law 3.4 Passive Power Factor Correction Methods 3.4.1 Improving Harmonics by Reducing the Filter Capacitance of Rectifier Filter Circuits 3.4.2 Passive PFC 3.4.2.1 Passive PFC with Inductor on the AC Side | . 11<br>. 15<br>. 18<br>e<br>. 19<br>. 21<br>. 21<br>. 23<br>. 25<br>. 27 |

|    | 3.5 Active Power Factor Correction Methods 3.5.1 Low Frequency Active PFC 3.5.2 High Frequency Active PFC 3.5.2.1 Buck Converter Based Active PFC 3.5.2.2 Boost Converter Based Active PFC 3.5.2.3 Buck-Boost Converter Based Active PFC 3.6 The Future of Power Factor Correction                                                       | . 29<br>. 31<br>. 32<br>. 34                                              |

|    | o the filling of Power Exclor Correction                                                                                                                                                                                                                                                                                                 | 14                                                                        |

| 4. | 4. A Novel Power Factor Correction Scheme                  |    |  |  |

|----|------------------------------------------------------------|----|--|--|

| 5. | <b>Power Electronics Considerations</b>                    | 43 |  |  |

|    | 5.1 The CCM Boost Converter                                | 44 |  |  |

|    | 5.2 MOSFET Switching Speed Considerations and EMI          | 50 |  |  |

|    | 5.3 Comparing the CCM and CRM PFC Converter                | 54 |  |  |

|    | 5.4 Continuous Conduction Mode Power Factor Correction     | 57 |  |  |

|    | 5.5 Optimizing Performance of CCM PFC Circuits             | 60 |  |  |

|    | 5.5.1 Optimizing Selection of Power Devices                | 61 |  |  |

|    | 5.5.2 Optimizing Inductor Design                           | 62 |  |  |

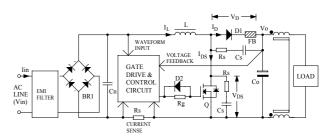

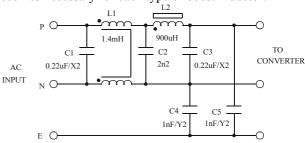

|    | 5.5.3 Optimizing EMC issues                                |    |  |  |

| 6. | A 1200 W Active PFC Prototype                              | 65 |  |  |

|    | 6.1 Converter Block Schematics                             | 66 |  |  |

|    | 6.2 Construction, Schematic Design and Component Selection | 68 |  |  |

|    | 6.3 PCB Layout Considerations and EMI                      | 76 |  |  |

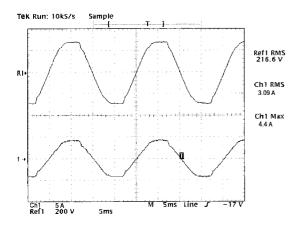

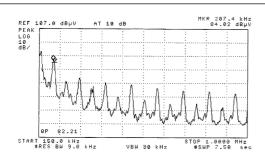

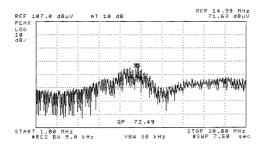

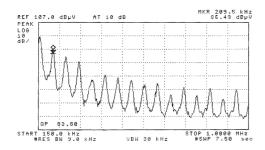

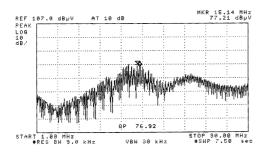

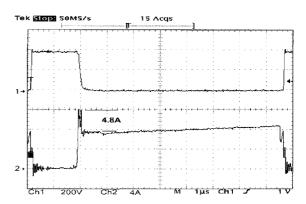

|    | 6.4 Oscillograms, EMI Measurements and Test reports        | 79 |  |  |

|    | 6.5 Other Experiments and Various Results                  | 84 |  |  |

| 7. | Conclusion                                                 | 85 |  |  |

|    | 7.1 Future Research                                        | 87 |  |  |

| 8. | References                                                 | 89 |  |  |

| 9. | Appendix                                                   | 93 |  |  |

|    | 9.1 List of Materials                                      | 93 |  |  |

|    | 9.2 Publications                                           | 98 |  |  |

## Chapter 1

### Introduction

Most electronic equipment is supplied by 50 Hz or 60 Hz utility power, and in almost all of them power is processed through some kind of a power converter. Usually, power converters use a diode rectifier followed by a bulk capacitor to convert AC voltage to DC voltage. It is predicted that more than 60% of utility power will be processed through some form of power electronics equipment by the year 2010. Most of this equipment will have a rectifier with capacitive filter circuit front end. Unless some correction circuit is used, the input rectifier with a capacitive filter circuit will draw pulsating currents from the utility grid resulting in poor power quality and high harmonic contents that adversely affect other users. The situation has drawn the attention of regulatory bodies around the world. Governments are tightening regulations, setting new specifications for low harmonic current, and restricting the amount of harmonic current that can be generated. As a result, there is a need for a reduction in line current harmonics necessitating the need for power factor correction (PFC) and harmonic reduction circuits.

Improvements in power factor and harmonic distortion can be achieved by modifying the input stage of the diode rectifier filter capacitor circuit. Passive solutions can be used to achieve this objective for low power applications. With a filter inductor connected in series with the input circuit, the current conduction angle of the single-phase full-wave rectifier is increased leading to a higher power factor of about 0.8 and lower input current distortion. With smaller values of inductance, these achievements are degraded. However, the large size and weight of these elements, in addition to their inability to achieve unity power factor or lower current distortion significantly, make passive power factor correction more suitable at lower power levels.

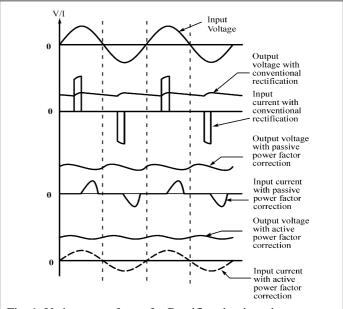

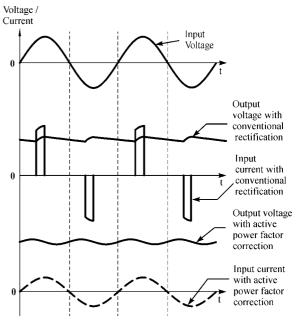

Active PFC solutions are a more suitable option for achieving near unity power factor and sinusoidal input current waveform with extremely low harmonic distortion. In these active solutions, a converter with switching frequencies higher than the AC line frequency is placed between the

output of the diode bridge rectifier and the bulk capacitor. The reactive elements of this converter are small, because their size depends on the converter switching frequency rather than the AC line frequency. The function of this converter is to make the load behave as an ideal resistive load and thus eliminate the generation of line current harmonics. However, adding a high frequency switching converter in series with the input circuit naturally causes a reduction in overall efficiency of the whole converter due to the losses contributed by this active PFC circuit. Moreover, the active PFC circuit contributes to an increase in overall costs, increase in EMI, and reduction in reliability due to an increase in the number of components.

An active PFC circuit obviously forms a very important part of any AC-DC converter today. It is, therefore, of even greater importance that the cost and performance of these active PFC circuits should be optimized.

### 1.1 Problem Overview and Research Goals

The preceding discussion on the need for Power Factor Correction (PFC), tightening regulations restricting the amount of harmonic current that can be generated, Power Factor Correction methods, and the need to use the high frequency continuous conduction mode active PFC circuit for higher power converters demonstrates the need for further research in these areas. Specifically, the following three areas need to be addressed.

In Europe it is now required by law that any equipment that can be connected to the public mains network has to satisfy the EN 61000 3-2 requirements of limiting the input line current harmonics. As unity power factor is not required by this standard, limiting the input current harmonics is enough. However, with many amendments to this standard, it is important to understand the standard and evaluate PFC techniques that helps meet the standard and also optimize overall cost and performance.

Any active PFC converter provides input power factor correction and generates a regulated boosted high voltage DC for a world-wide AC input range between 85 V to 270 V. The initial total cost of limiting the input current harmonics and providing power factor correction can be large. Today, PFC circuits are being widely used for applications needing converters with power rating greater than 300 W. It is important, therefore, to understand and investigate the possibility of having a

common power factor correction circuit for an installation and thus save costs. The CCM PFC converter is the preferred choice for this as this topology is more suitable for medium to high power applications.

With the active CCM PFC converter being the most commonly used PFC topology for medium to high power applications, another objective is to investigate the various power electronics issues of the CCM PFC converter and thus evolve methods that can optimize cost and performance of these PFC circuits.

The aim of this research work is to investigate the need for PFC circuits including identifying new applications that help reduce harmonic currents and optimize performance and costs of high-frequency active PFC circuit topologies. The focus is to investigate methods to improve EMI, improve efficiency and optimize the size of the boost inductor in a CCM PFC circuit. Thus the overall objective of this thesis is to develop methods that reduce overall system costs and improve performance and cost of CCM PFC circuits.

### 1.2 Previous Work

A lot of work has been done on various PFC circuit topologies and lately, there has been an immense active interest in single stage PFC [1.1,1.2] circuits that generate an isolated DC output. The single aim of all the above work has been to reduce cost [1.3] and optimize performance of active PFC circuits. Industrial PFC digital controllers are also now available [1.4] and sometimes used. Dedicated analog single stage PFC controllers [1.5] and resonant PFC controllers [1.6,1.7] are also used in the power electronics industry.

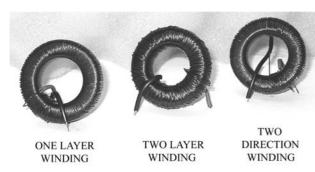

In spite of all these developments, the CCM mode PFC circuit is still the most popular due to its excellent overall performance. Some work has been done earlier on EMI [1.8] performance, boost inductor winding methods [1.9] and boost diode recovery related losses [1.10]. This dissertation attempts to work further on these areas.

## Chapter 2

### Aim of the Work and Contribution

The aim of this thesis is to understand the need for power factor correction towards meeting tightening regulations that restrict the amount of harmonic currents that can be generated. Moreover, another goal is to also understand the need to use active PFC circuits, particularly high frequency CCM PFC circuits for higher power converters, and improve performance of these converters. Thus, the final objective is to develop methods that improve performance and reduce overall costs of systems with PFC circuits. To meet these objectives, various problem areas were identified and the research results published in various international journals and conferences.

### 2.1 Specific Problem Areas and Publications

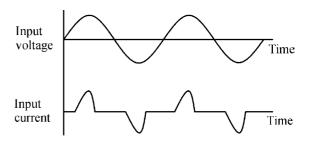

Most modern electronic apparatus use some form of AC to DC power conversion within their architecture and it is these power converters that draw pulses of current from the AC network during each half cycle of the supply waveform. The amount of reactive power drawn by a single apparatus (a domestic television for example) may be small, but within a typical street there may be a hundred or more TV sets or other types of equipment drawing reactive power from the same supply phase, resulting in a significant amount of reactive current flow and generation of harmonics. The effect of poor power factor and harmonics generated by equipment that can be connected to the public mains network is a matter of concern today. Thus Harmonics must be filtered and this has led to the creation of the EN 61000-3-2 standard and its adoption by the European Community. The standard does not require the load power factor to be unity and requires only limiting of the input current harmonics.

**Paper A** discusses the causes of input current distortion in AC-DC single phase rectifier-capacitor filter circuits and provides an understanding of the mandatory low-frequency harmonic limits of the European standard EN 61000-3-2 that is applicable to these circuits. Different Power Factor Correction (PFC) techniques and strategies useful for meeting this

standard and mitigate this problem, are explored in this paper. Some simulations and measurement results are also presented.

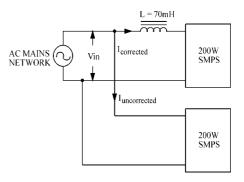

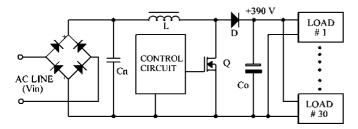

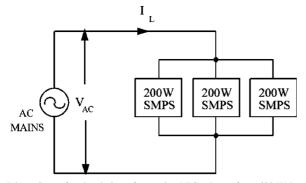

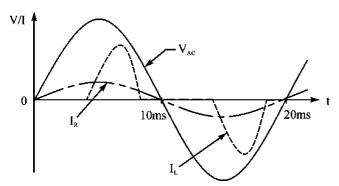

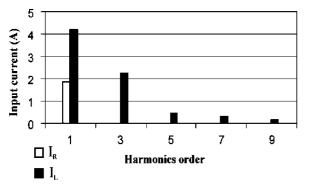

These PFC techniques and strategies include the use of passive PFC chokes and active PFC circuits. The most commonly used PFC topology for medium to high power applications that provides input power factor correction and generates a regulated boosted high voltage DC in the face of varying input AC between 85 V to 270 V, is the CCM boost converter. Based on this CCM boost converter, **Paper B** proposes a novel central power factor correction scheme. In this paper, the disadvantages of having a passive power factor correction circuit to meet the mandatory EN 61000-3-2 standard and the advantages of having a common central power factor correction scheme over having individual active or passive power factor correction circuits, are investigated and documented. Higher reliability and the ability of this common central power factor correction scheme to provide an in-built uninterrupted power supply (UPS) with automatic universal worldwide operation for all loads connected to it, are highlighted.

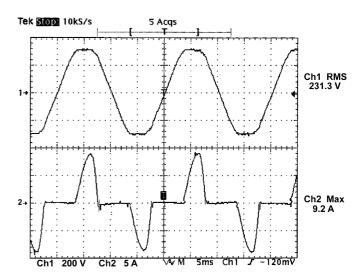

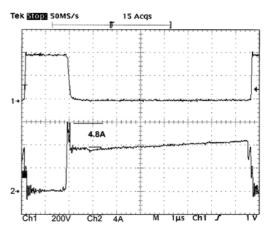

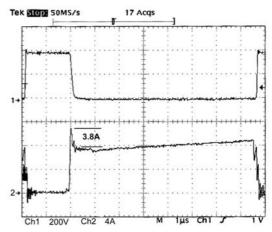

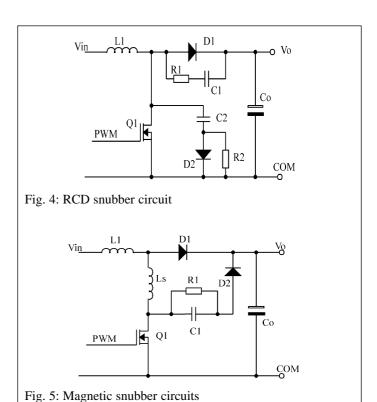

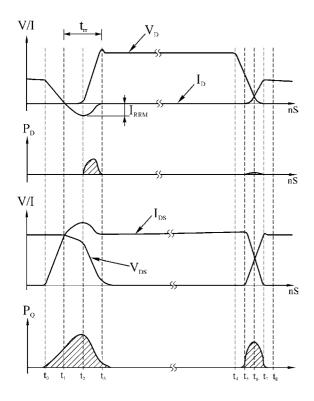

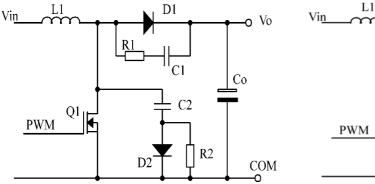

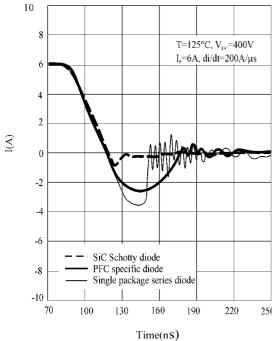

Applications today demand significantly increased power densities of up to 18 W / cubic inch. Thus designers today constantly seek efficiency optimization in every part of their design. Moreover, increasing power densities require an increase in the switching frequency and reduction in size of EMI components. Thus, understanding and control of specific power electronics issues is an important prerequisite towards optimizing the cost and performance of these PFC circuits. Paper C and Paper D explore ways, including the use of SiC diodes, to increase the efficiency and switching frequency of continuous mode boost PFC circuits. The dependence of electrical and thermal performances of these PFC circuits on the characteristics of the power switching devices is studied. By making measurements on a practical 600 W and 1000 W PFC circuit prototype, these papers show how every specific application would need a unique design solution to optimize cost and performance.

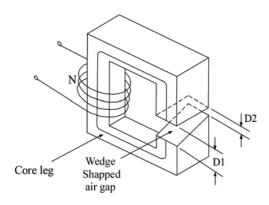

In a CCM boost PFC converter, the boost inductor design is usually straight forward but the variables that decide the size of this inductor are usually difficult to quantify and often depend heavily on the designers choice. **Paper E** explores the effect of these variables on the overall performance of a PFC converter, by making extensive measurements of conducted EMI, inductor temperature rise and converter efficiency. Three inductance design values are compared and verified with measurements on a 1200 W prototype operating at about 70 kHz. Based on these measurements, a systematic design approach is suggested.

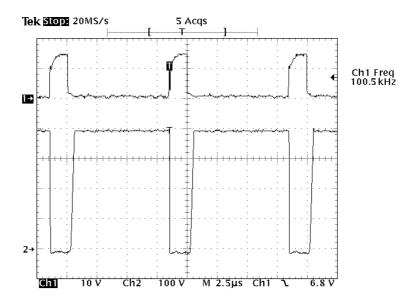

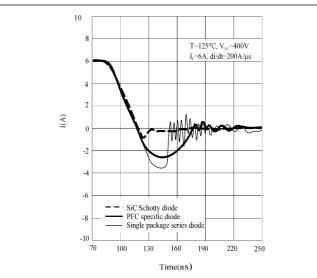

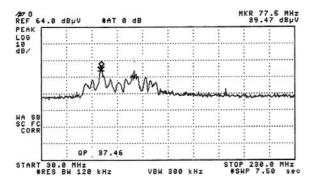

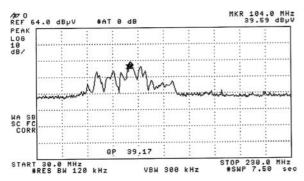

For a CCM boost PFC converter, the boost rectifier diode ratings can be computed easily while the selection of the diode recovery characteristics is usually always decided by the final cost and efficiency requirements of the design. By making extensive measurements on a 600 W and 1000 W prototype operating at about 100 kHz, **Paper F** explores the effect of diode recovery characteristics and its snap factor characteristics for three different diode types, on the overall EMI and efficiency performance of a CCM boost PFC converter.

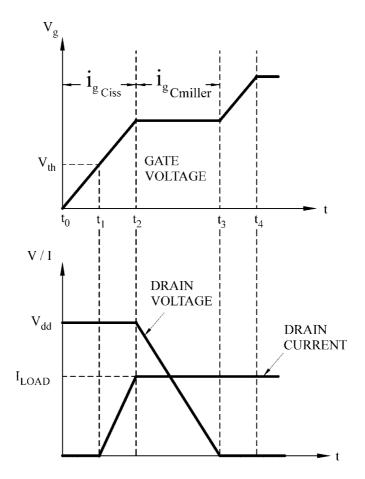

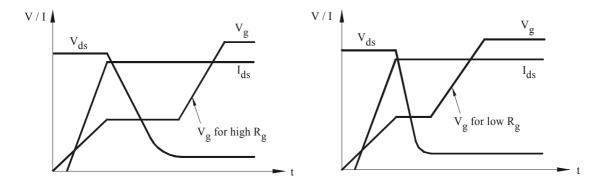

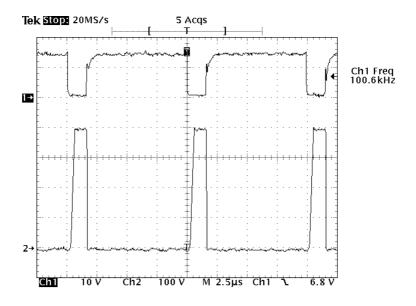

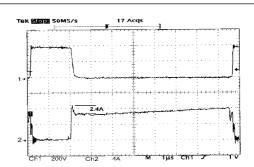

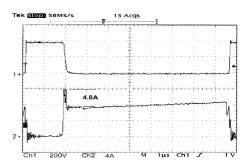

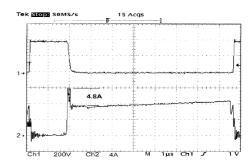

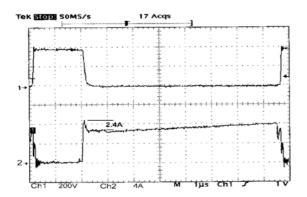

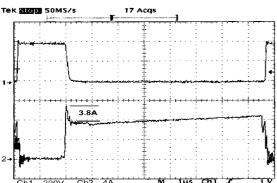

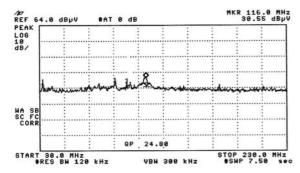

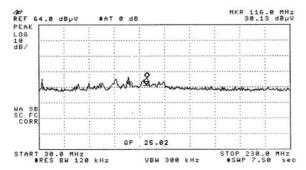

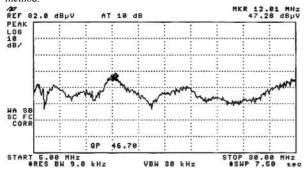

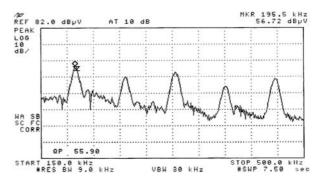

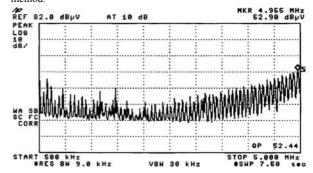

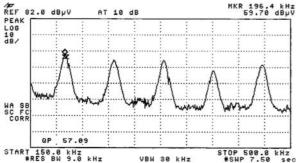

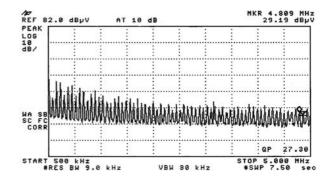

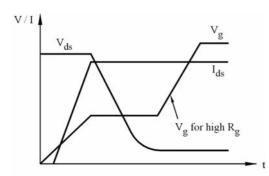

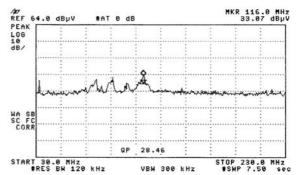

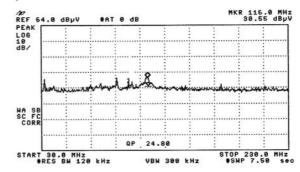

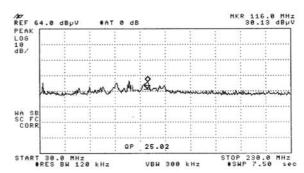

The switching speed of a Power MOSFET being user controllable, faster switching speeds reduce switching losses and improve efficiency. However, excessive di/dt due to fast switching would cause current overshoots, ringing and boost rectifier recovery current spikes leading to generation of large EMI. It is also commonly known that the snappier the diode's recovery characteristics, the higher would be the generated EMI. Thus Silicon Carbide (SiC) diodes with zero recovery time is expected to generate the least EMI. **Paper G** and **Paper I** explores the effect of these variables on the overall performance of a 1000 W prototype PFC Converter operating at about 100 kHz. By making extensive measurements of conducted / radiated EMI and converter efficiency, for different MOSFET switching speeds and diode types, a systematic design approach is suggested by which higher switching speeds required for higher efficiency and higher frequency operation, does not significantly increase the generated EMI.

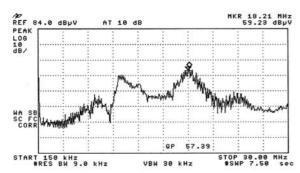

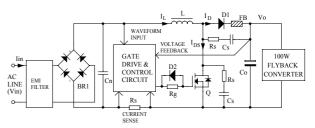

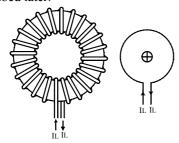

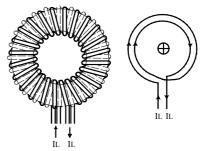

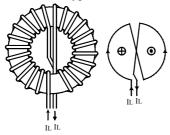

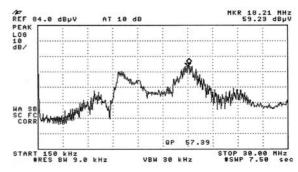

The radiated fields emanating from the boost inductor, due to the type of core used or winding direction or winding method, couple to the EMI filter and other components and induce differential mode and common mode noise. The worst case is when a gapped magnetic core is used for the inductor. Moreover, increased turns for achieving higher inductance, necessary for reducing inductor ripple current for improving efficiency, result in winding overlap in the inductor and this increases the inter winding capacitance of the inductor resulting in higher noise feedthrough. Paper H explores the effect of these variables on the overall performance of a 100 W AC-DC Converter prototype with a PFC Converter operating at about 70 kHz and a downstream discontinuous flyback converter synchronized to the PFC converter. By making extensive measurements of conducted and radiated EMI, for various winding schemes, a systematic novel design approach is highlighted by which it was possible to reduce conducted EMI by more than 23 dBuV for a 100 W converter.

## Chapter 3

### **Need for Power Factor Correction and Solutions**

With most electronic equipment being connected to the electricity distribution network, the non-sinusoidal input line current drawn by these equipment due to input line rectification generates current harmonics that causes severe problems. These include increased magnitudes of neutral currents in three-phase systems, overheating of transformers and induction motors. This creates the need for some kind of power conditioning. Thus, the need to limit the harmonic content of line currents drawn by electronic equipment connected to the electricity distribution networks, results in the need for *Power Factor Correction - PFC*.

### 3.1 Definitions

Power factor is defined as the ratio of the average power to the apparent power drawn by a load from an AC source. Assuming an ideal sinusoidal input voltage source, the power factor can be expressed as the product of the distortion power factor and the displacement power factor, as given in (3.1). The distortion power factor  $K_d$  is the ratio of the fundamental root-mean-square (RMS) current  $(I_{rms(1)})$  to the total RMS current  $(I_{rms})$ . The displacement power factor  $K_\theta$  is the cosine of the displacement angle between the fundamental input current and the input voltage [3.1].

$$PF = K_d K_\theta \tag{3.1}$$

The distortion power factor  $K_d$  is given by the following equation.

$$K_d = I_{rms(1)} / I_{rms} \tag{3.2}$$

The displacement power factor  $K_{\theta}$  is given by the following equation.

$$K_{\theta} = \cos \theta \tag{3.3}$$

The displacement power factor  $K_{\theta}$  can be made unity with a capacitor or inductor but making the distortion power factor  $K_d$  unity is more difficult. When a converter has less than unity power factor, it means that the converter absorbs apparent power that is higher than the active power it consumes. This implies that the power source should be rated to a higher VA rating than what the load needs. In addition, the current harmonics generated by the converter deteriorates the power quality [3.2] of the source, which eventually affects other equipment.

High power factor and low harmonics do not go hand-in-hand. Though there is no a direct correlation between the two, the following equations link total harmonic distortion *(THD)* to power factor in some way.

THD (%)=

$$100 \times \sqrt{\frac{1}{K_d^2} - 1}$$

(3.4)

The distortion power factor  $K_d$  is also given by the following equation.

$$K_{d} = \frac{1}{\sqrt{1 + \left(\frac{THD(\%)}{100}\right)^{2}}}$$

(3.5)

Therefore, when the fundamental component of the input current is in phase with the input voltage,  $K_{\theta} = 1$ . We then have,

$$PF = K_d K_\theta = K_d \tag{3.6}$$

Substituting (3.5) in (3.6), we have

$$PF = \frac{1}{\sqrt{1 + \left(\frac{THD(\%)}{100}\right)^2}}$$

(3.7)

Moreover, a perfectly sinusoidal current could also have a poor power factor if its phase was not in line with the voltage. From (3.7) it is apparent that a 10% THD corresponds to a Power Factor of approximately 0.995. Thus it is clear that specifying limits for each of the harmonics will help in the control of input current "pollution" better, both from the standpoint of minimizing the circulating currents and reducing the interference with other equipment. So, while the process of shaping this input current is commonly called "power factor correction," the measure of its effectiveness towards complying with international regulations is the amount of reduction in the harmonic content of the input current.

### 3.2 Need for Power Factor Correction

### The Off-Line Rectifier

The input stage of any AC-DC converter comprises of a full-bridge rectifier followed by a large filter capacitor. The input current of such a rectifier circuit comprises of large discontinuous peak current pulses that result in high input current harmonic distortion. The high distortion [3.3] of the input current occurs due to the fact that the diode rectifiers conduct only for a short period. This period corresponds to the time when the mains instantaneous voltage is greater than the capacitor voltage.

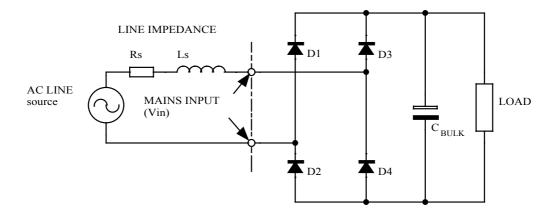

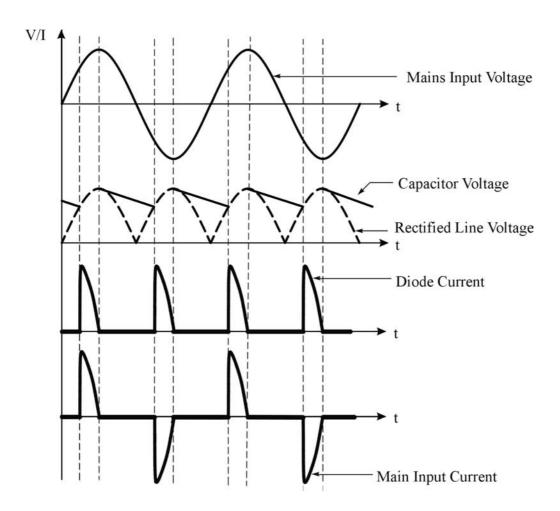

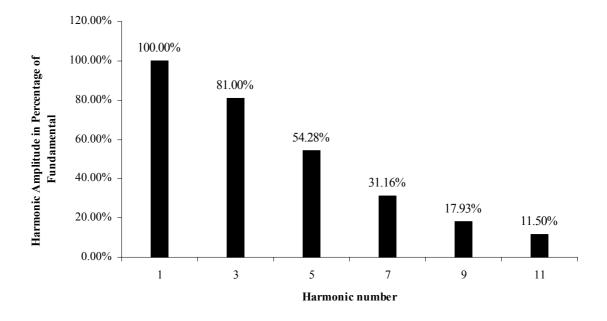

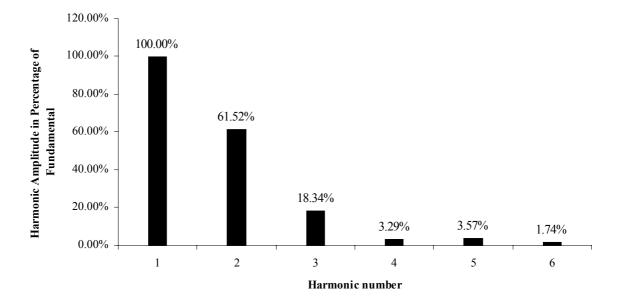

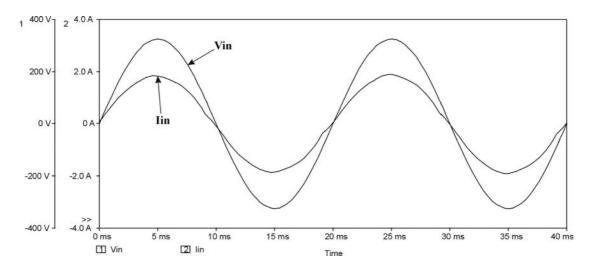

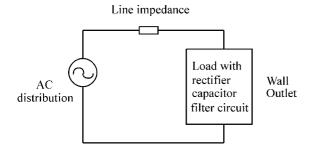

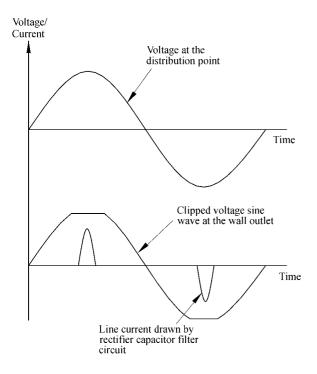

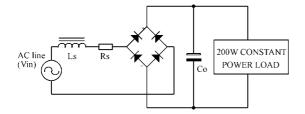

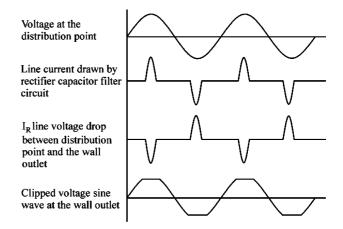

Since the instantaneous mains voltage is greater than the capacitor voltage only for very short periods of time, when the capacitor is fully charged, large current pulses are drawn from the line during this short period of time. The typical input current harmonic distortion for this kind of rectification is usually in the range of 55% to 65% and the power factor is about 0.6. **Fig. 3.1a** shows the schematic of a typical single-phase diode rectifier filter circuit while **Fig. 3.1b** shows the typical simulated line voltage and current waveforms. The actual current wave shape and the resulting harmonics depend on the line impedance. **Fig. 3.1c** and **Fig. 3.1d** show the simulated odd line current harmonics normalized to the fundamental for different line impedance values.

Fig. 3.1a. Typical input stage schematic of an off-line switching power supply.

Fig. 3.1b. Typical line current and voltage waveforms.

**Fig. 3.1c.** Odd line current harmonics normalized to the fundamental for the condition when the load is near the distribution transformer resulting in higher harmonic currents due to lower input line impedance.

**Fig. 3.1d.** Odd line current harmonics normalized to the fundamental for the condition when the load is away from the distribution transformer resulting in lower harmonic currents due to higher input line impedance.

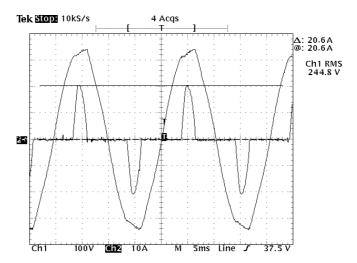

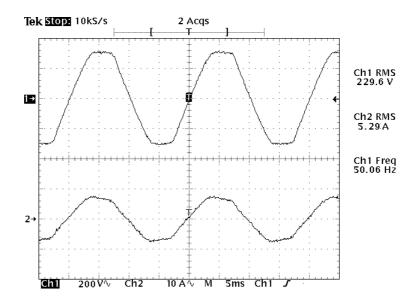

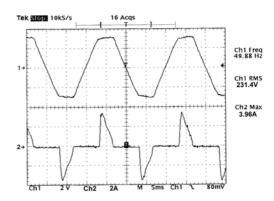

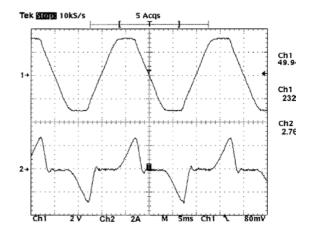

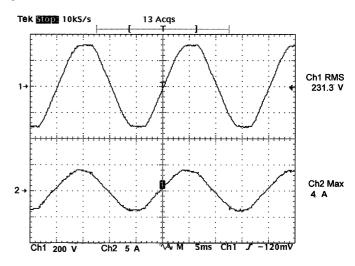

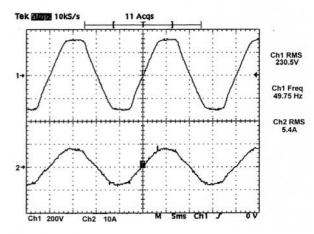

Practical measurements were made with a 1 kW constant power load comprising of a switch mode AC-DC converter. To emulate a low line impedance condition, measurements were made at a location near to the distribution transformer. The observed input voltage and current drawn by the converter is shown in the oscillogram of **Fig. 3.1e**. Channel 1 shows the input voltage while Channel 2 shows the input current. It can be seen that the input peak current is very high and is about 20 A. The corresponding input voltage peak is also distorted due to the drop in the line impedance caused by this peak current.

**Fig. 3.1e.** Voltage and current waveforms for a 1 kW constant power load for the condition when the load is near the distribution transformer resulting in higher input peak currents due to lower input line impedance.

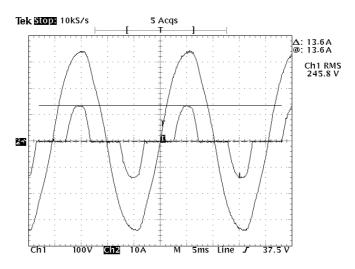

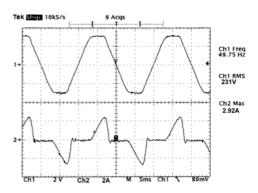

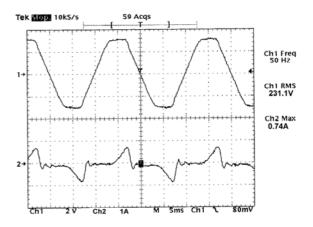

After this, measurements were made for the same 1 kW constant power load comprising of a switch mode AC-DC converter, at a location far away from the distribution transformer. This emulated a higher line impedance condition. The observed input voltage and current drawn by the converter is shown in the oscillogram of **Fig. 3.1f**. Channel 1 shows the input voltage while Channel 2 shows the input current. It can be seen that the input peak current is now much lower, to about 13 A. It can be observed that the corresponding input voltage peak is now also much less distorted due to this reduced peak current.

**Fig. 3.1f.** Voltage and current waveforms for a 1 kW constant power load for the condition when the load is away from the distribution transformer resulting in lower input peak currents due to higher input line impedance.

Conventional AC rectification is thus a very inefficient process, resulting in waveform distortion of the current drawn from the mains. This produces a large spectrum of harmonic signals that may interfere with other equipment [3.4, 3.5, 3.6]. A circuit similar to that shown in **Fig. 3.1a** is used in most mains-powered AC-DC converters. At higher power levels (200 to 500 watts and higher) severe interference with other electronic equipment may become apparent due to these harmonics sent into the power utility line. Another problem is that the power utility line cabling, the installation and the distribution transformer, must all be designed to withstand these peak current values resulting in higher electricity costs for any electricity utility company.

Thus, summarizing, conventional AC rectification has the following main disadvantages:

- It creates harmonics and electromagnetic interference (EMI).

- It has poor power factor.

- It produces high losses.

- It requires over-dimensioning of parts.

- It reduces maximum power capability from the line.

## 3.3 Requirements as Per Law

Thus, the harmonics generated as a result of conventional AC rectification must be filtered and this has prompted a need for setting limits for the line current harmonics generated by equipment connected to the electricity distribution network. Standardization activities in this area have been carried out for many years. As early as 1982, the International Electrotechnical Committee (IEC) published its standard IEC 555-2, which was also adopted in 1987 as the European standard EN 60555-2, by the European Committee for Electrotechnical Standardization (CENELEC). The IEC 555-2 Standard was later replaced in 1995 by the IEC 1000-3-2 standard and subsequently adopted by CENELEC as the European standard EN 61000-3-2 [3.7].

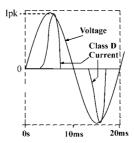

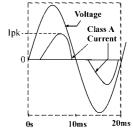

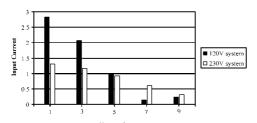

Today, in Europe, compliance to the EN 61000-3-2 is a legal requirement. After many amendments, the standard today applies to any equipment with a rated current up to and including 16A RMS per phase and which is to be connected to the 50Hz, 230V single-phase or 400V three-phase mains network. Depending on the type of equipment and its probable frequency of daily usage, all electrical equipment are categorized into four classes, namely, Class A, B, C and D. Specific maximum limits are set for the harmonic content of the line current drawn by the equipment. Of these, the Class D limits are the most difficult to meet, as the limit depends on the equipment's power rating and applies to equipment that is connected to the utility network for a significant part of its life cycle resulting in the greatest impact on the power supply network. Personal computers and television sets are examples of such equipment. Also, an important waiver is that other than lighting equipment, limits do not apply for equipment with rated power of 75 W or less (it may be reduced to 50 W in the future).

Thus, any equipment connected to the public utility grid in the European Union is covered by these four classes. Each class has its own set of limits for harmonic currents. Briefly, these different limits are as under: *Class A equipment:* All equipment that does not fit into the other three classes are categorized as Class A equipment. This class set the absolute maximum current values allowed for each harmonic and these are given in **Table 3.1**. Limits do not change with equipment rating.

Class B equipment: All portable tools are categorized as Class B equipment. Harmonic current limits are absolute maximum values. As power tools are used infrequently/for short periods, Class B limits are the least restrictive and set the absolute maximum current allowed for each harmonic to 1.5 times the Class A limits.

Class C equipment: All lighting products, including dimming devices, with an active input power higher than 25 W are categorized as Class C equipment. There are limits on the second harmonics and also on all odd harmonics. The limits are expressed in terms of the fundamental current's percentage. The maximum current percentage allowed for each harmonic, to meet Class C limits, is shown in **Table 3.2**.

Class D equipment: All equipment like computers and television sets that are frequently used for longer periods are categorized as Class D equipment. The limits depend on the power rating of the equipment. The current limit for Class D is expressed in terms of mA per Watt of the power consumed. Thus, the acceptable limit of the harmonic current being generated by a load is proportional to its power rating. Hence, low power equipment have a lower absolute limit of harmonic current. These limits are given in **Table 3.1**.

**Table 3.1**: EN 61000-3-2, Class A & Class D Harmonic Current limits

|                       | Class A                                  | Class D                                    |                                            |  |  |

|-----------------------|------------------------------------------|--------------------------------------------|--------------------------------------------|--|--|

| Harmonic order (n)    | Absolute<br>limit<br>(No Power<br>limit) | Relative limit<br>(600 W ≥ Power<br>>75 W) | Absolute limit<br>(600 W ≥<br>Power >75 W) |  |  |

| 01401 (11)            | Maximum permissible harmonic             | Maximum permissible harmonic current       | Maximum permissible harmonic               |  |  |

|                       | current (A)                              | per watt (mA/W)                            | current (A)                                |  |  |

|                       | Odd Harmonics                            |                                            |                                            |  |  |

| 3                     | 2.30                                     | 3.4                                        | 2.30                                       |  |  |

| 5                     | 1.14                                     | 1.9                                        | 1.14                                       |  |  |

| 7                     | 0.77                                     | 1.0                                        | 0.77                                       |  |  |

| 9                     | 0.40                                     | 0.5                                        | 0.40                                       |  |  |

| 11                    | 0.33                                     | 0.35                                       | 0.33                                       |  |  |

| 13                    | 0.21                                     |                                            |                                            |  |  |

| $15 \le n \le 39$     |                                          | Use following equations                    |                                            |  |  |

| (Class A)             |                                          |                                            |                                            |  |  |

| $13 \le n \le 39$     | 2.25/n                                   | 3.85/n                                     | 2.25/n                                     |  |  |

| (Class D)             |                                          |                                            |                                            |  |  |

| <b>Even Harmonics</b> |                                          |                                            |                                            |  |  |

| 2                     | 1.08                                     |                                            |                                            |  |  |

| 4                     | 0.43                                     |                                            |                                            |  |  |

| 6                     | 0.30                                     | Not Appl                                   | icable                                     |  |  |

| $8 \le n \le 40$      | 1.84/n                                   |                                            |                                            |  |  |

| (Class A)             |                                          |                                            |                                            |  |  |

**Table 3.1.** Limits for Class A and Class D equipment.

**Table 3.2**: EN 61000-3-2, Class C Harmonic Current limits

|          | Harmonic Current limits                  |

|----------|------------------------------------------|

| Harmonic | Maximum permissible harmonic             |

| order    | current expressed as a percentage of the |

| (n)      | input current at the fundamental         |

|          | frequency                                |

| 2        | 2                                        |

| 3        | $30 \times \text{circuit power factor}$  |

| 5        | 10                                       |

| 7        | 7                                        |

| 9        | 5                                        |

| 11≤n≤39  | 3                                        |

**Table 3.2.** Limits for Class C equipment.

**Paper A** discusses in detail the causes of input current distortion in AC-DC single phase rectifier- capacitor filter circuits and the mandatory low-frequency harmonic limits of the European standard EN 61000-3-2. Different Power Factor Correction (PFC) techniques / strategies useful for complying with the standard are discussed in detail.

For higher power and higher voltage applications, the IEEE 519-1992 Standard [3.8] gives recommended practices and requirements for harmonic control in electrical power systems, for both individual consumers and utilities. The limits for line current harmonics are given as a percentage of the maximum fundamental frequency component of the load current demand I<sub>L</sub>, at the Point of Common Coupling in the utility. The limits depend on the short-circuit current at the Point of Common Coupling resulting in lower limits for weaker grids. However, since standards are evolving, changes can be expected in the future.

### 3.4 Passive Power Factor Correction Methods

As described earlier in **Section 3.1**, power factor depends on both harmonic content and displacement power factor. Moreover, the EN 61000-3-2 standard sets limits on the harmonic content of the load current and does not specifically regulate the power factor or the total harmonic distortion of the line current. In consideration of the above, the following can be concluded.

- A high power factor can be achieved even with a substantial harmonic content. The power factor is not significantly degraded by harmonics, unless its amplitude is quite large.

- Low harmonic content does not guarantee high power factor.

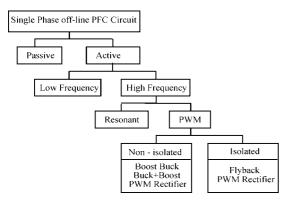

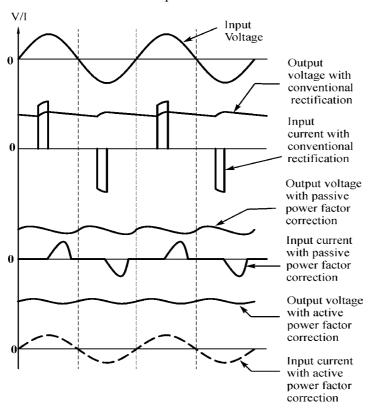

Thus, PFC circuits for nonlinear loads have their primary goal to reduce the harmonic content of the line current. PFC circuit solutions can be broadly categorized as *passive* or *active* circuits. In *passive* PFC, only passive elements are used in addition to the diode bridge rectifier, to improve the shape of the line current. The output voltage is not regulated and it follows the line variations. In *active* PFC, active switches are used in conjunction with inductors. The output voltage is usually regulated for line variations. The switching frequency further differentiates the active PFC solutions into two classes, the *low-frequency* and the *high-frequency* active PFC. In *low-frequency* active PFC circuits, the switching is synchronized to the line voltage. In *high-frequency* active PFC circuits, the switching frequency is much higher than the line frequency.

# 3.4.1 Improving Harmonics by Reducing the Filter Capacitance of Rectifier Filter Circuits

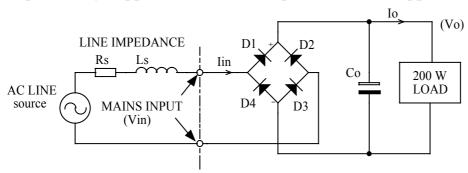

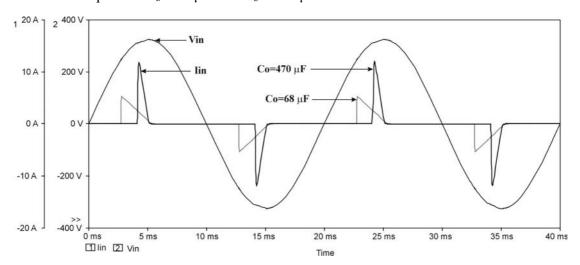

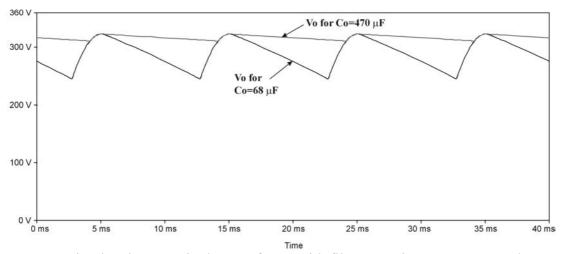

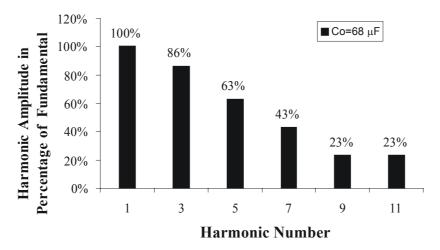

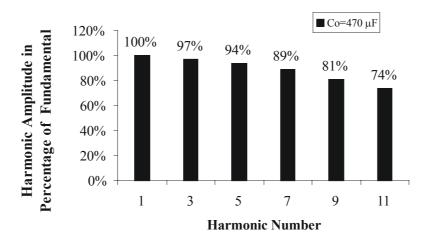

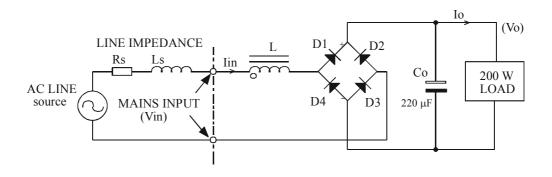

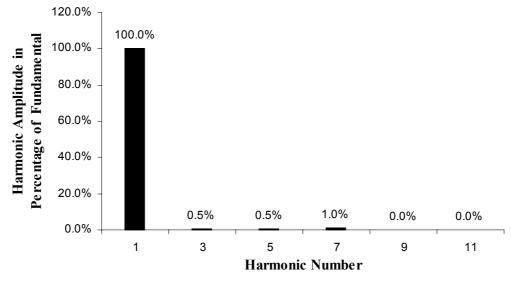

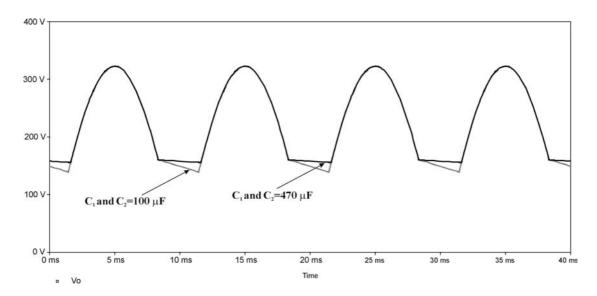

**Fig. 3.2a** shows the schematic of a typical single-phase diode rectifier filter circuit. The simplest way to improve the shape of the line current for this circuit is to use a lower filter capacitance. This increases the output DC voltage ripple but helps increase the rectifier conduction interval resulting in a lower input peak current. This also helps in reducing the harmonic content and improves the power factor but this is far from the ideal solution. For a constant power load with output capacitor values of  $68~\mu F$  and  $470~\mu F$ , the simulated input current waveforms are shown in **Fig. 3.2b** while the output ripple waveforms is shown in **Fig. 3.2c**. For each of these filter capacitor values, the odd line current harmonics are normalized to the fundamental and shown in **Fig. 3.2d** and **Fig. 3.2e** respectively. This scheme has such severe limitations since it does not substantially reduce the harmonic currents and the high output voltage ripple makes it unacceptable for most applications.

**Fig. 3.2a.** Schematic of a typical single-phase rectifier filter circuit with filter capacitor  $C_0 = 68 \mu F$  and  $C_0 = 470 \mu F$ .

**Fig. 3.2b.** Simulated input voltage and current waveforms with filter capacitor  $C_o$ = 68  $\mu F$  and  $C_o$ = 470  $\mu F$ .

**Fig. 3.2c.** Simulated output ripple waveforms with filter capacitor  $C_o$ = 68  $\mu$ F and  $C_o$ = 470  $\mu$ F.

It is apparent from above that in this scheme the output ripple increases as the output capacitor is reduced. Usually, this increased output ripple is not a major concern at low power levels since the load is usually a switch mode converter and it can easily adjust its duty cycle to deliver a constant load power.

Fig. 3.2d. Odd line current harmonics normalized to the fundamental with filter capacitor  $C_o$ = 68  $\mu$ F.

Fig. 3.2e. Odd line current harmonics normalized to the fundamental with filter capacitor  $C_0$ = 470  $\mu$ F.

### 3.4.2 Passive PFC

Passive PFC circuits use additional passive components in conjunction with the diode bridge rectifier. Various combinations of these passive components in different circuit locations give rise to many possible schemes. Only those schemes that are commonly used are covered in the following sections.

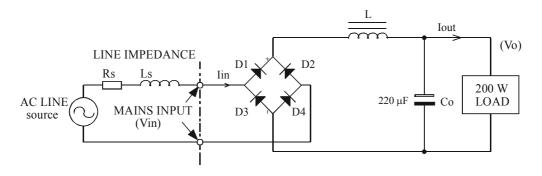

### 3.4.2.1 Passive PFC with Inductor on the AC Side

As shown in **Fig. 3.3a**, one of the simplest and popular methods to achieve PFC is to add an inductor on the AC side of the diode bridge in series with the line voltage. This improves the power factor considerably along with the reduction in the input current harmonics. Achieving a power factor of about 0.82 is practical. The output voltage is not regulated and the output DC voltage ripple increases with load. Popularly this is known as the passive PFC [3.9] and today it is possible to buy these inductors off the shelf.

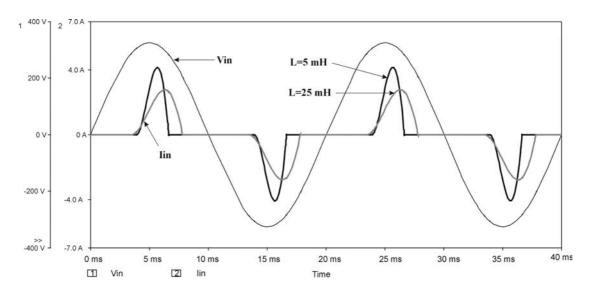

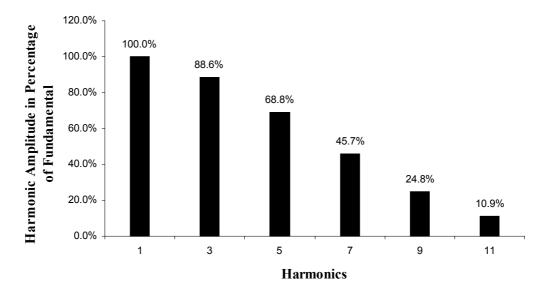

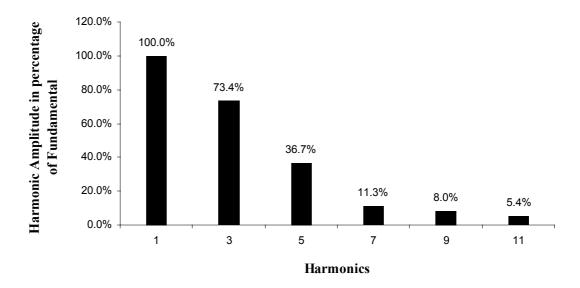

The simulated input current waveforms for a 200 W constant power load, are shown in **Fig. 3.3b** for inductance values of 5 mH and 25 mH. For each of these inductance values, the odd current harmonics normalized to the fundamental is shown in **Fig. 3.3c** and **Fig. 3.3d** respectively.

**Fig. 3.3a.** Typical schematic of a single-phase rectifier filter circuit with passive PFC circuit.

**Fig. 3.3b.** Simulated current and voltage waveforms for a 200 W constant power load with passive PFC circuit and inductance values of 5 mH and 25 mH.

**Fig. 3.3c.** Odd line current harmonics normalized to the fundamental for a 200W constant power load with passive PFC circuit and 5 mH inductance.

**Fig. 3.3d.** Odd line current harmonics normalized to the fundamental for a 200W constant power load with passive PFC and inductance value of 25mH.

### 3.4.2.2 Passive PFC with Inductor on the DC Side

For the next scheme shown in **Fig. 3.4a**, the inductor is placed on the DC side [3.10, 3.11]. If the inductor current is continuous for a given load current, the power factor can be as high as 0.9. Of course, this requires a relatively large inductance. When the inductor current becomes discontinuous due to reduction in load or when a lower inductance value is used, the input current wave shape becomes similar to that shown in **Fig. 3.3b** and the power factor also deteriorates to about 0.8.

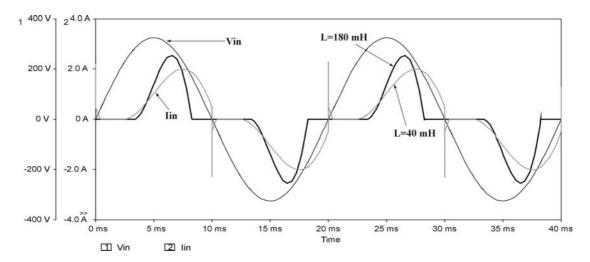

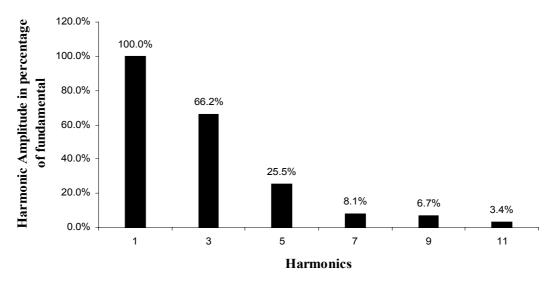

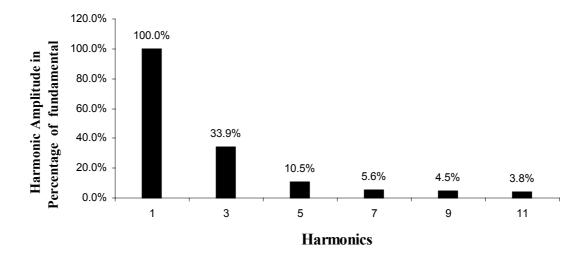

For a 200 W constant power load with inductance values of 40 mH and 180 mH, the simulated input current waveforms are shown in **Fig. 3.4b**. For each of these inductors, the odd current harmonics normalized to the fundamental is shown in **Fig. 3.4c** and **Fig. 3.4d** respectively.

**Fig. 3.4a.** Typical schematic of a single-phase rectifier filter circuit with passive PFC circuit and the inductor on DC side.

**Fig. 3.4b.** Simulated input current and voltage waveforms for a 200 W constant power load with passive PFC circuit and the inductor on the DC side for with inductance values of 40 mH and 180 mH.

**Fig. 3.4c.** Odd line current harmonics normalized to the fundamental for a 200 W constant power load with passive PFC circuit and the inductor on the DC side with inductance value of 40 mH.

**Fig. 3.4d.** Odd line current harmonics normalized to the fundamental for a 200 W constant power load with passive PFC circuit and the inductor on the DC side with inductance value of 180 mH.

There are also several solutions based on resonant networks. When introduced in-between the AC source and the load, these attenuate the harmonics. Examples include a series resonant type band-pass filter tuned at the line-frequency or a parallel-resonant type band-stop filter tuned at the third harmonic. However, these solutions are not commonly used due to the large values of inductance and capacitance required for these networks.

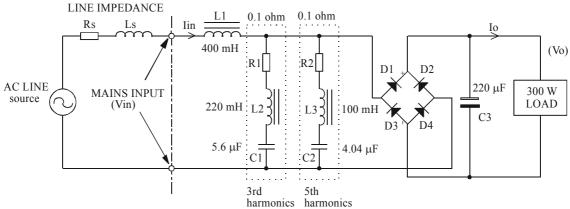

## 3.4.2.3 Passive PFC with Harmonic Trap Filter

Another solution that is often used is a harmonic trap filter. This consists of a series resonant network, connected in parallel to the AC source and tuned to the harmonic frequency that must be attenuated. Usually two harmonic traps are used and these are tuned at the dominant 3<sup>rd</sup> and 5<sup>th</sup> harmonics. **Fig. 3.5a** shows the schematic of this scheme with a constant power load of 300 W. Here too, the output voltage is not regulated and the output DC voltage ripple increases with load. This scheme is not investigated in detail as it is expensive, requires large inductors and is frequency sensitive.

Simulated input current and input voltage waveforms for a harmonic trap filter based PFC scheme is shown in **Fig. 3.5b.** The odd line current harmonics normalized to the fundamental is shown in **Fig. 3.5c**. It can be seen that this scheme gives excellent power factor and input current wave shape at the expense of large reactive components.

**Fig. 3.5a.** Typical schematic of a single-phase rectifier filter circuit with harmonic trap filter for passive PFC circuit.

**Fig. 3.5b.** Simulated input current and voltage waveforms for a 300 W constant power load with harmonic trap filter for passive PFC circuit.

**Fig. 3.5c**. Odd line current harmonics normalized to the fundamental for a 300 W constant power load with harmonic trap filter for passive PFC circuit.

## 3.4.2.4 Passive PFC using Valley Fill Rectifier

**Fig. 3.6a** represents the schematic for a 200W constant power load valley-fill rectifier [3.12]. The circuit reduces the harmonic content of the line current but the output voltage varies significantly because of the large output ripple voltage. This solution is often used for lighting ballast circuits [3.13].

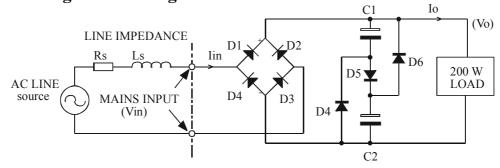

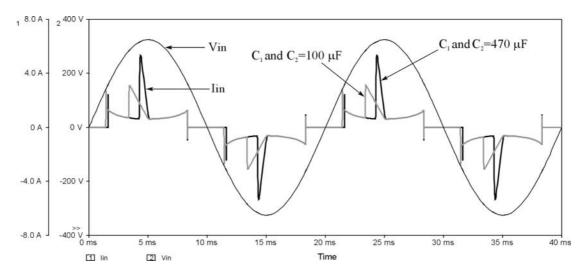

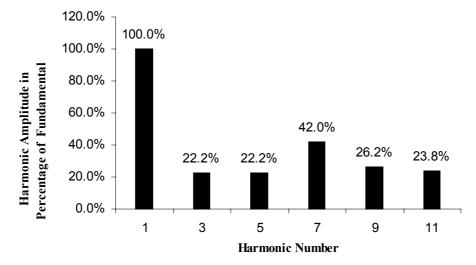

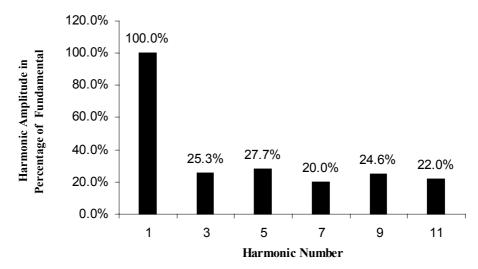

Simulated input current and voltage waveforms for a valley fill rectifier based PFC scheme with a 200 W constant power load and two different capacitance values of 470  $\mu$ F and 100  $\mu$ F, is shown in **Fig. 3.6b** while the output voltage waveforms are shown in **Fig. 3.6c**. For these capacitance values, the odd line current harmonics normalized to the fundamental is shown in **Fig. 3.6d** and **Fig. 3.6e**.

**Fig. 3.6a.** Typical schematic of a single-phase rectifier filter circuit for a valley fill rectifier based passive PFC circuit.

**Fig. 3.6b.** Simulated input current and voltage waveforms with a 200 W constant power load for a valley fill rectifier based passive PFC circuit with capacitance values of  $100 \, \mu F$  and  $470 \, \mu F$ .

Fig. 3.6c. Simulated output voltage waveform with a 200 W constant power load for a valley fill rectifier based passive PFC circuit with capacitance values of  $100~\mu F$  and  $470~\mu F$ .

Fig. 3.6d. Odd line current harmonics normalized to the fundamental with a 200W constant power load for a valley fill rectifier based passive PFC circuit with capacitance value of  $100~\mu F$ .

Fig. 3.6e. Odd line current harmonics normalized to the fundamental with a 200W constant power load for a valley fill rectifier based passive PFC circuit with a capacitance value of 470  $\mu$ F.

### 3.4.2.5 Limitations of Passive PFC Circuits

The simplicity, reliability, insensitivity to noise and surges and the non-generation of any high-frequency EMI offered by passive power factor circuits are of significant usefulness. However, the bulky size of these filters, their poor dynamic response, complexity and high cost, the lack of voltage regulation and their sensitivity to line-frequency, limits their use to below 200 W applications. Moreover, even though line current harmonics are reduced, the fundamental component may show an excessive phase shift resulting in reduction in power factor.

### 3.5 Active Power Factor Correction Methods

Active PFC circuits that have better characteristics and do not have many of the above drawbacks are reviewed in the following sections.

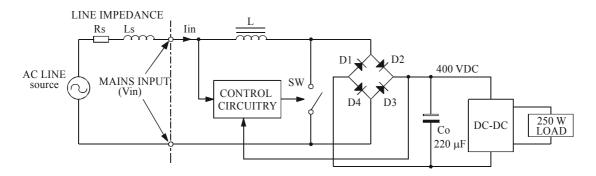

# 3.5.1 Low Frequency Active PFC

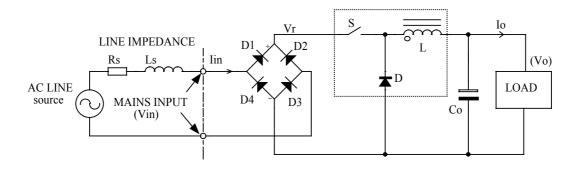

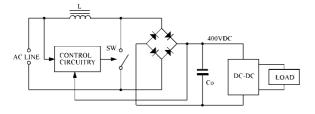

An active low frequency PFC circuit for a 250W constant power load is shown in **Fig. 3.7a**. Input Power factors as high as 0.95 can be achieved with an active low frequency PFC circuit design. In this scheme, the switch (SW) is bi-directional and it is operated for a constant period after the line voltage zero crossing. After this constant on-period after the line voltage zero crossing or when the output voltage tries to increase beyond

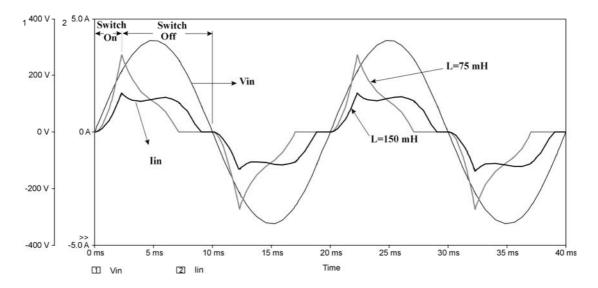

the set limits, this switch (SW) is turned off. This forces an increase in the conduction angle [3.14] of the input bridge rectifiers, giving rise to an acceptable current waveform. Simulated input current and voltage waveforms for an active low frequency PFC circuit with a 250 W constant power load and two different inductance values of 150 mH and 75 mH, is shown in **Fig. 3.7b**. The odd line current harmonics normalized to the fundamental is shown in **Fig. 3.7c** and **Fig. 3.7d**.

This scheme has the advantage that it generates less EMI, requires a smaller inductor when compared to the passive PFC and the simple low frequency circuit is more reliable and efficient when compared to the active high frequency PFC scheme described later.

However, when compared to the high frequency active PFC circuit, the reactive elements are larger and the regulation of the output voltage is slower.

Fig. 3.7a. Typical schematic of a low frequency active PFC circuit.

**Fig. 3.7b.** Simulated input current and voltage waveforms for a 250 W constant power load with low frequency active PFC circuit and inductance values of 75 mH and 150 mH.

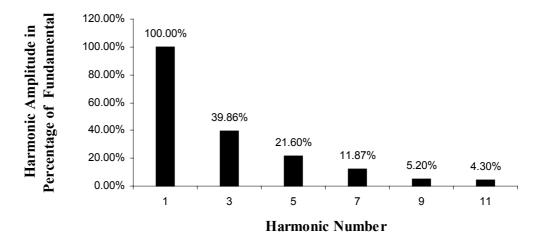

**Fig. 3.7c**. Odd line current harmonics normalized to the fundamental with a 250 W constant power load for a low frequency active PFC circuit with an inductance value of 75 mH.

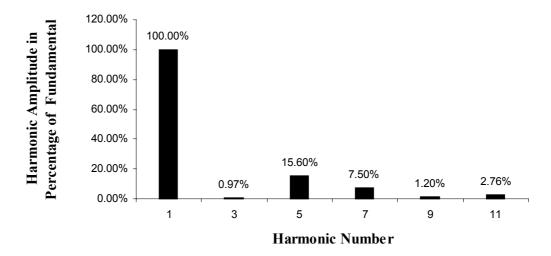

**Fig. 3.7d**. Odd line current harmonics normalized to the fundamental with a 250 W constant power load for a low frequency active PFC circuit with an inductance value of 150 mH.

## 3.5.2 High Frequency Active PFC

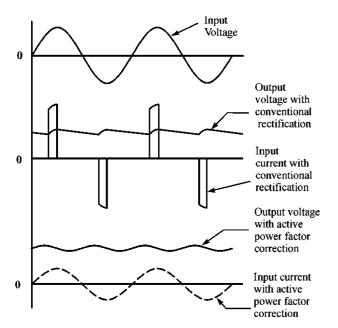

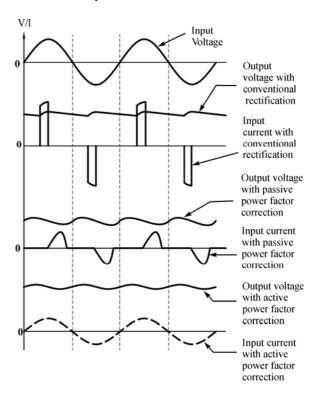

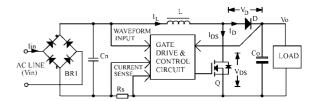

The high frequency active PFC circuit can be realized by placing a buck or a boost or a buck-boost converter in between the bridge rectifier and the filter capacitor of a conventional rectifier filter circuit and operating it by a suitable control method that would shape the input current. For all converter topologies, the switching frequency is much higher than the line-frequency, the output voltage ripple is twice the line-frequency and the output DC is usually regulated.

The PFC output voltage can be higher or lower, depending on the type of converter being used. With a buck converter the output voltage can be lower, for a boost converter the output voltage can be higher, while for a buck-boost converter the output voltage can be higher or lower than the maximum amplitude of the input voltage. The inductor current in these converters can be either continuous or discontinuous. In the continuous conduction mode (CCM) the inductor current never reaches zero during one switching cycle while in the discontinuous conduction mode (DCM), the inductor current is zero during intervals of the switching cycle. However, though the inductor current can be continuous in all the three types of converters, the high frequency switching current components of the AC input current can be continuous only in the case of the boost converter. This is because for the buck and the buck-boost converter, the converter switch interrupts the input current in every switching cycle.

This is apparent from the operating characteristics of each converter described below. The given waveforms are representative and shown only for explanation of the topology specific characteristics. In reality, the switching frequency is much higher than the line-frequency and the input AC current waveform is dependent on the type of control being used. The inductors are assumed to be in the CCM of operation.

### 3.5.2.1 Buck Converter Based Active PFC

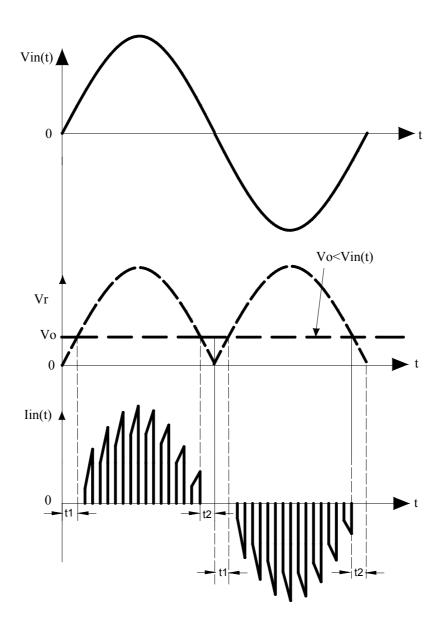

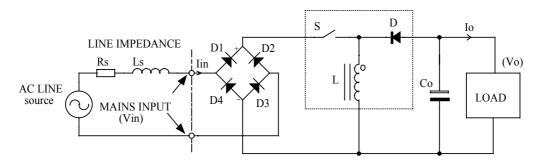

A buck converter based PFC circuit that steps down the input voltage is shown in **Fig. 3.8a** and **Fig. 3.8b** shows its associated waveforms. However since the converter can operate only when the instantaneous input voltage  $V_{in(t)}$  is higher than the output voltage  $V_o$ , there is no current flow from the AC input during the period  $t_1$  and  $t_2$ . This gives the line current envelope a distortion near the input voltage zero crossing. Moreover, even if the inductor current is continuous, the input switching current of the converter is discontinuous as the high frequency switch S interrupts the input current during every switching cycle. Thus, the input current has significant high-frequency components that increases EMI and filtering requirements.

Fig. 3.8a. Buck converter based high frequency active PFC circuit.

Fig. 8b Current and voltage waveforms of a Buck converter based PFC circuit.

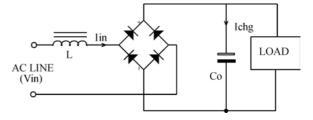

### 3.5.2.2 Boost Converter Based Active PFC

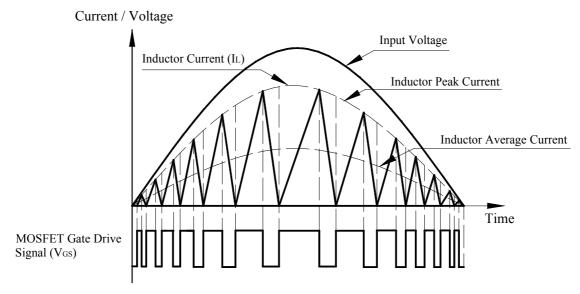

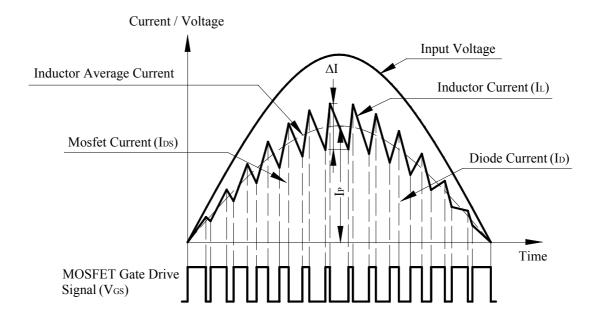

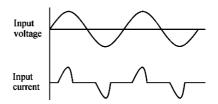

The boost converter, the most common topology used for power factor correction, can operate in two modes – continuous conduction code (CCM) and discontinuous conduction mode (DCM). The transition mode control, also referred to as critical conduction mode (CRM) or boundary conduction mode, maintains the converter at the boundary between CCM and DCM by adjusting the switching frequency.

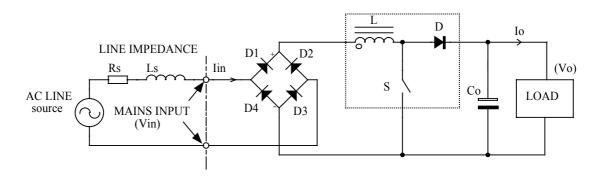

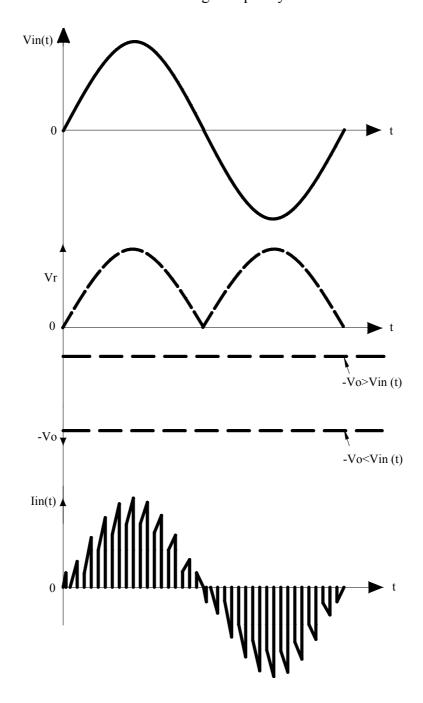

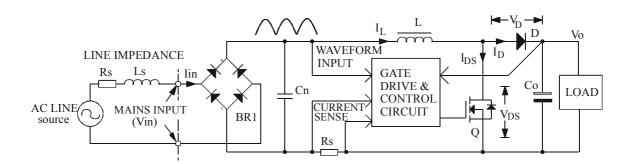

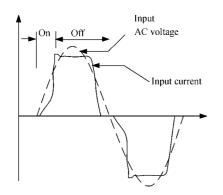

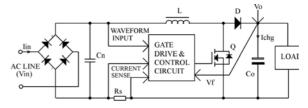

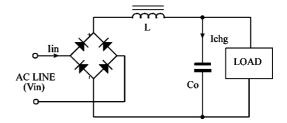

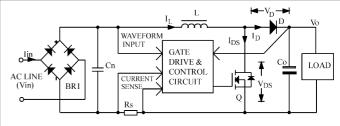

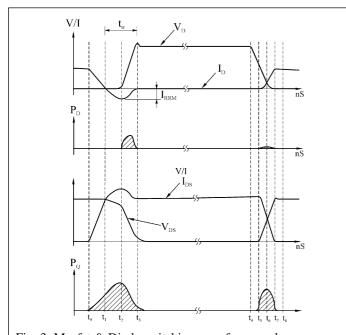

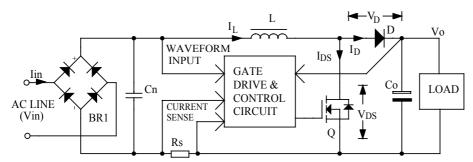

A CCM boost converter based PFC circuit and its associated waveforms are shown in Fig. 3.9a and Fig. 3.9b.

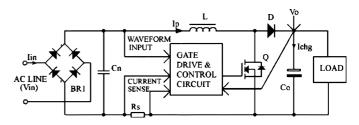

Fig. 3.9a. Boost converter based high frequency active PFC circuit.

This topology steps up the input voltage. Since the converter can operate throughout the line-cycle, the input current does not have crossover distortions. This gives the line current envelope no distortion near the input voltage zero crossing. Moreover, the input switching current of the converter is continuous as the boost inductor is placed in series with the input, and the high frequency switch S does not interrupt the input current. Thus, the input current has lesser high-frequency components resulting in lower EMI and reduced filtering requirements. The output capacitor  $C_o$  limits the switch S's turn-off voltage to almost the output voltage through diode D and thus protects the switch.

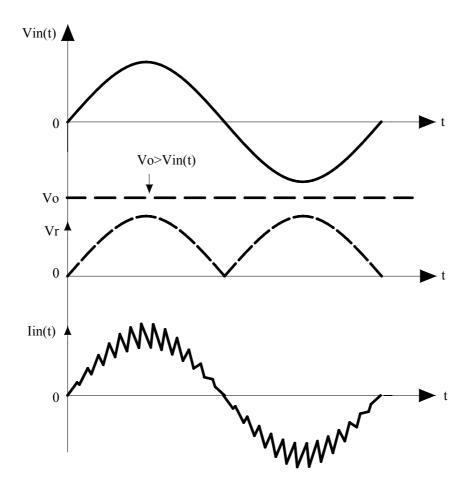

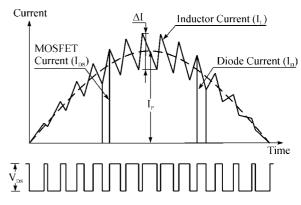

**Fig. 3.9b.** Current and voltage waveforms of a CCM boost converter based PFC circuit.

In the above converter, the control scheme can force the current in the inductor to be either continuous or discontinuous. The DCM converter operates at fixed frequency and has switching current discontinuities in comparison to the CCM or CRM techniques. Due to the large peak currents and EMI associated with the DCM converter, it is rarely or never used. These large peak currents are due to the dead time needed at certain instantaneous input voltages to remain discontinuous over all input line variations. On the other hand the CRM converter typically uses a variation of hysteretic control with the lower boundary equal to zero current. It is a variable frequency control technique that has an inherently stable input current control while eliminating reverse recovery rectifier losses. For a given set of input and output parameters, the on-time remains the same, but the off- time is varied. The result of this is that the switching frequency of the power converter, is highest when the instantaneous input voltage is the lowest, and vice versa.

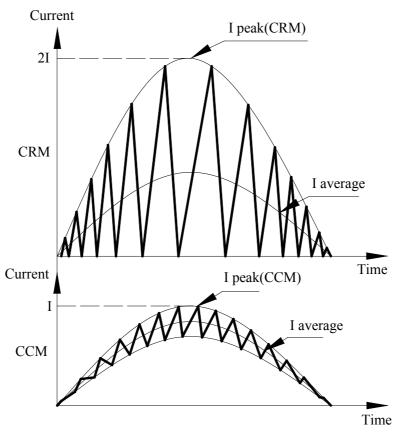

The power stage equations and the transfer functions of the CRM converter are the same as the CCM converter. Transition mode forces the inductor current to operate just at the border of CCM and DCM. The current profile is also different and affects the component power loss and filtering requirements. The peak current in the CRM boost converter is twice the amplitude of the CCM boost converter leading to higher conduction losses. The peak-to-peak ripple is twice the average current, which affects MOSFET switching losses and AC losses in the boost inductor. The main trade-off in using the CRM boost converter is lower losses due to no reverse recovery in the boost diode at the expense of higher inductor ripple and peak currents. As presented in **Paper C**, with the present availability of very fast diodes, this issue is now a declining concern for designers today.

For medium to higher power applications, where the input filter requirements dominate the size of the magnetics, the CCM boost converter is a better choice due to lower peak currents (which reduces conduction losses) and lower ripple current (which reduces input filter requirements and inductor AC losses).

For these reasons, the CCM converter is popular and used widely for PFC circuit applications where the power rating is greater than 100 W.

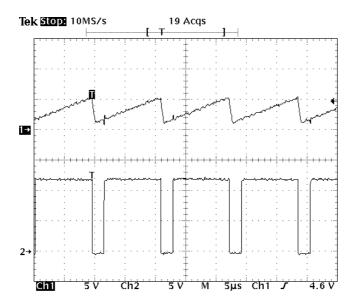

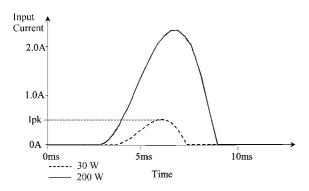

The inductor current for a 100 W converter operating in the CCM and CRM mode, are compared in **Fig. 3.10**. The peak inductor current is shown as  $I_{peak}$  while the average inductor current is shown as  $I_{average}$ .

Fig. 3.10. Comparison of inductor current for CCM and CRM operating modes.

### 3.5.4.3 Buck-Boost Converter Based Active PFC

Lastly, the buck-boost converter based PFC circuit and its associated waveforms are shown in **Fig. 3.11a** and **Fig. 3.11b**. This can step up or step down the input voltage. The output voltage is inverted, which translates into higher voltage stress for the switch. Since the converter can operate throughout the line-cycle, the input current does not have crossover distortions. This gives the line current envelope no distortion near the input voltage zero crossing. However, even if the inductor current is continuous, like the buck converter, the input switching current of the converter is discontinuous as the high frequency switch S interrupts the input current. Thus, the input current has significant high-frequency components that increases EMI and filtering requirements.

Fig. 3.11a. Buck-boost converter based high frequency active PFC circuit.

**Fig. 3.11b.** Current and voltage waveforms of buck-boost converter based PFC circuit.

### 3.6 The Future of Power Factor Correction

Today PFC techniques are being increasingly used in most new off-line power converter designs. This is motivated both by the concerns listed above and by the regulatory requirements, and this is an overall positive development for equipment users and the power utilities. Most PFC circuits are now active rather than passive, and while this results in exceptional PFC performance, it requires that additional circuitry be added. The added circuitry can have the following negative impacts on the system:

- Additional cost and complexity for the power converter.

- Lower power converter reliability due to additional components.

- Slightly lower efficiency due to additional conversion stage.

In spite of these limitations, including an active PFC is most often a very good design trade-off for the power system. The above concerns are usually more than offset by the reduced input current, undistorted current waveforms, universal input operation and additional useful power capability of converters that utilize PFC.

Thus, active power factor correction is an emerging need for all AC-DC converter designs, and optimizing cost and performance of these continuous mode PFC circuits is the need of the day.

# Chapter 4

## **A Novel Power Factor Correction Scheme**

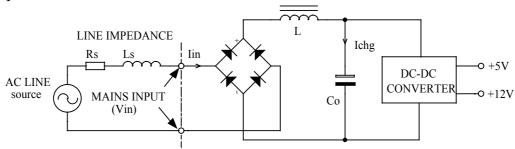

As discussed earlier, the internal circuits of most small electronic equipment does not work directly from the rectified supply voltage derived from the mains network. Instead an in built DC-DC converter converts the rectified high voltage derived from the mains network to much lower isolated voltages like 5 V or 12 V, usable directly by the equipment's internal semiconductor circuits.

**Fig. 4.1** Simplified block diagram of the input circuit of most small electronic equipment.

**Fig. 4.1** represents a simplified block diagram of the input circuit of most small electronic equipment. The mains voltage is rectified to get an unregulated high voltage across the filter capacitor,  $(C_o)$ . The harmonic currents generated by the charging of this capacitor are attenuated by the series connected choke (L), to provide passive power factor correction. Assuming a line variation of 230 V  $\pm$  20 %, the DC voltage across the filter capacitor would vary between the  $V_{in(min)}$  and  $V_{in(max)}$  limits given below.

$$V_{in(min)} = 0.8 \times 230 \times \sqrt{2}$$

= 260 V (4.1)

$$V_{in(max)} = 1.2 \times 230 \times \sqrt{2}$$

= 390 V (4.2)

The downstream DC-DC converter in the above figure has a line regulation range from 260 V to 390 V. It is interesting to observe that these small electronic equipment would work equally well when connected to a DC power source [4.1] of any polarity, provided the output voltage of this DC source is between 260 V and 390 V. The input bridge

rectifier makes it practical for the equipment to work with DC input of any polarity. The passive power factor correction choke would have no function while operating with DC. Operation with DC naturally results in no harmonic currents at the input. Thus we can conclude that most small electronic equipment would work equally well with a DC voltage of about 390 V.

The common power factor correction scheme proposed in **Paper B** exploits this fact. It proposes to operate all small electronic equipment from a common central DC network or bus. With no limitation to the polarity of the input DC that may be connected to these equipment, it is practical to connect without any limitation as many devices as the DC source could support. The power rating for each device and the number of devices that the DC source would need to support will decide the total power rating of the DC source. The source of power for this DC source could be batteries or another AC-DC converter that generates harmonics, unless the common converter has an active power factor correction frontend at the input.

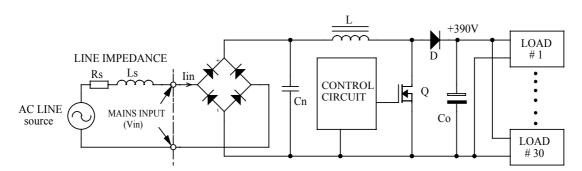

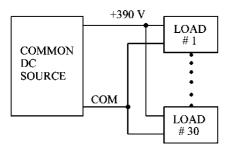

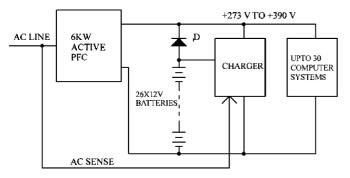

As shown in **Fig. 4.2**, a common active PFC circuit could be used for this DC source. The figure shows the simplified block diagram of the proposed scheme where thirty small electronic equipment work together. Using the same margins as discussed before, the voltage in the low voltage DC system could be between 260 V and 390 V.

Fig. 4.2. The Common active PFC circuit scheme.

Thus, we have a central common power factor correction scheme that runs thirty computer systems without generating any significant harmonic currents at unity power factor. Other advantages of having a common central power factor correction scheme is higher reliability, significant lower cost and an in-built uninterrupted power supply (UPS) with automatic universal worldwide operation of all loads connected to it. **Paper B** discusses these issues and the benefits of this scheme.

# Chapter 5

## **Power Electronics Considerations**

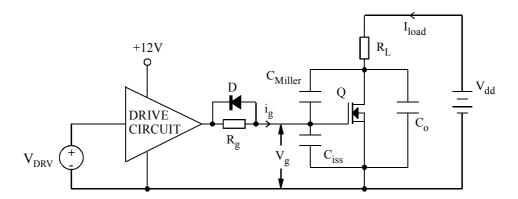

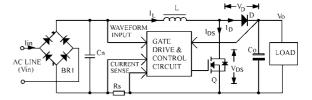

As described earlier, a variety of PFC circuit topologies [5.1] can be used which include the boost converter and the buck converter. Though soft switched Zero-Voltage-Transition (ZVT) techniques [5.2, 5.3] can be used for switching all the above topologies, the hard switched boost converter PFC circuit [5.4] is more popular due to its simplicity and ability to achieve a low distortion input current waveform. For reasons explained in **Section. 3.4.4.2**, the Continuous Conduction Mode (CCM) and Critical Conduction Mode (CRM) PFC circuit topologies are the most popular. However, both have their advantages and disadvantages. In the following section, the CCM boost converter is explained in detail. After this, the CRM and CCM PFC converters are compared.

As with all switch mode converter topologies, the only way to reduce size, improve power density and cost is to increase the switching frequency. However increasing the switching frequency brings along with it a set of well known problems that include increased EMI and losses. Similar problems also apply to the CCM PFC converter. Thus design optimization is a management of tradeoffs. For example, increasing MOSFET switching speed reduces switching losses but increases EMI while using a Silicon Carbide Schottky diode for the boost rectifier helps to reduce MOSFET turn-on losses but increases costs. Similarly, reducing the boost inductor ripple current improves efficiency and reduces EMI but increases the inductor size and cost. Again, increasing the total number of turns on the boost inductor reduces the inductor ripple current but increases EMI due to the increase in inter-winding capacitance of the overlapping turns. Thus an improvement in one area affects the performance of another. In this thesis, each of the components of a CCM PFC converter is investigated in detail and methods for optimization proposed.

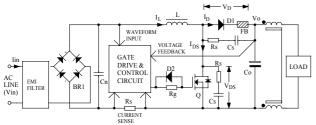

### **5.1** The CCM Boost Converter

Since the remaining part of the work is now based on a CCM PFC circuit, a detailed discussion on the boost converter is presented below.

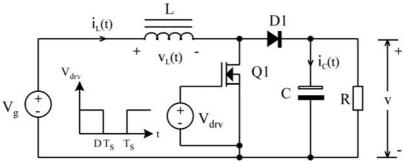

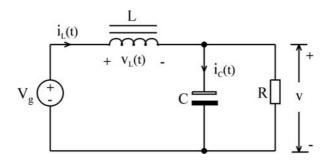

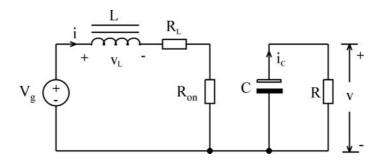

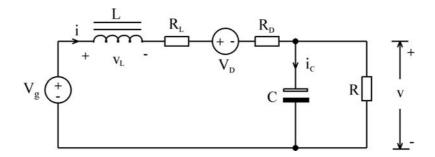

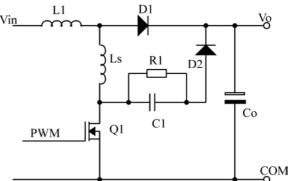

A CCM boost converter schematic is shown in the **Fig. 5.1a**. The equivalent circuit of the converter when the MOSFET turns on is shown in **Fig. 5.1b**, while **Fig. 5.1c** shows the condition when the MOSFET has turned off.

Fig. 5.1a Schematic of a CCM boost converter.

Fig. 5.1b Equivalent circuit of the CCM boost converter when Q1 turns ON.

Fig. 5.1c Equivalent circuit of the CCM Boost converter when Q1 turns OFF.

When the MOSFET Q1 turns on, one end of the inductor is connected to the input negative and diode D1 is reverse biased. The load current flows out of the charged output capacitor C.

Thus during this interval, the inductor voltage and capacitor current is,

$$v_L = V_g \tag{5.1}$$

$$i_C = -\frac{v}{R} \approx -\frac{V}{R} \tag{5.2}$$

When the MOSFET turns off, the inductor is connected to the output through the diode D1. Thus during this interval the inductor voltage and capacitor current is,

$$v_L = V_g - v \approx V_g - V \tag{5.3}$$

$$i_C = i_L - \frac{v}{R} \approx I - \frac{V}{R} \tag{5.4}$$

Using linear approximation, we assumed  $v \approx V$  and  $i_L = I$  in the above equations.

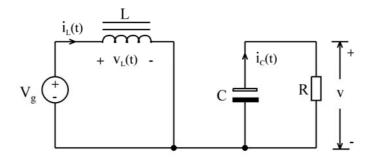

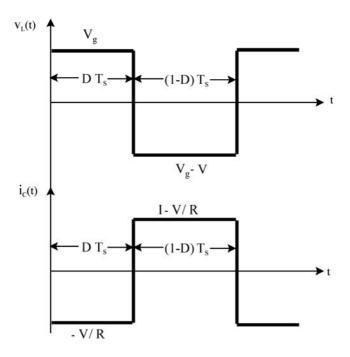

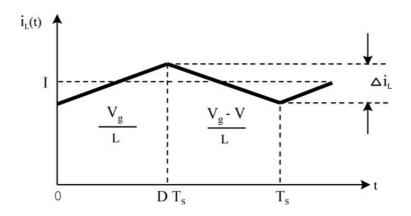

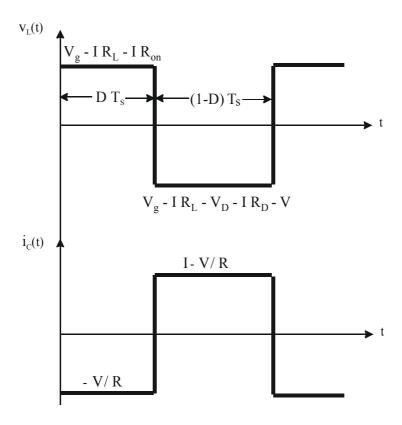

Now, from the above equations, the inductor voltage and capacitor current waveforms are plotted in **Fig. 5.2**. D is the on-time duty cycle of the MOSFET and  $T_s$  is the switching period.

Fig. 5.2 Inductor voltage and capacitor current wave forms.

The total volt-seconds applied to the inductor over one switching period is given by,

$$\int_{0}^{T_{S}} v_{L}(t)dt = (V_{g})DT_{S} + (V_{g} - V)(1 - D)T_{S}$$

(5.5)

Equating this expression to zero and collecting terms, we have

$$V_{\sigma}(D+1-D)-V(1-D)=0 (5.6)$$

$$V = \frac{V_g}{(1-D)} \tag{5.7}$$

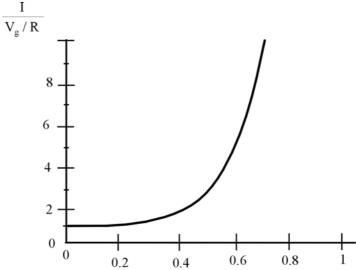

From the above, it is apparent that the output voltage increases as D increases. However, when component non-idealities are included, there is a limit to the maximum possible output voltage of a boost converter.

The DC component of the inductor current (I) is derived from the fact that the total charge on the output capacitor is always balanced. When the MOSFET turns on, the load current depletes the charge from the output capacitor while the capacitor recharges once the MOSFET turns off.

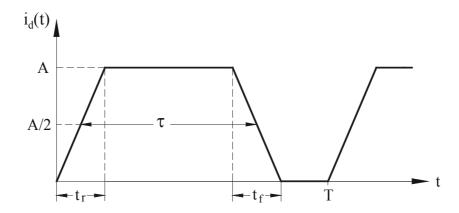

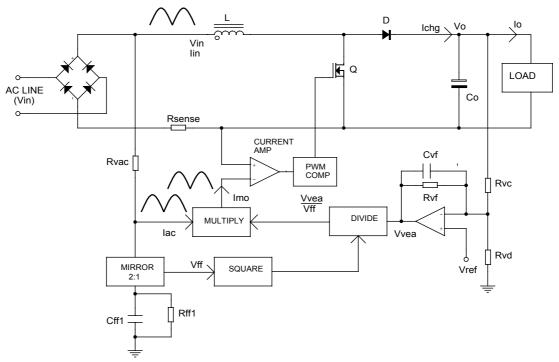

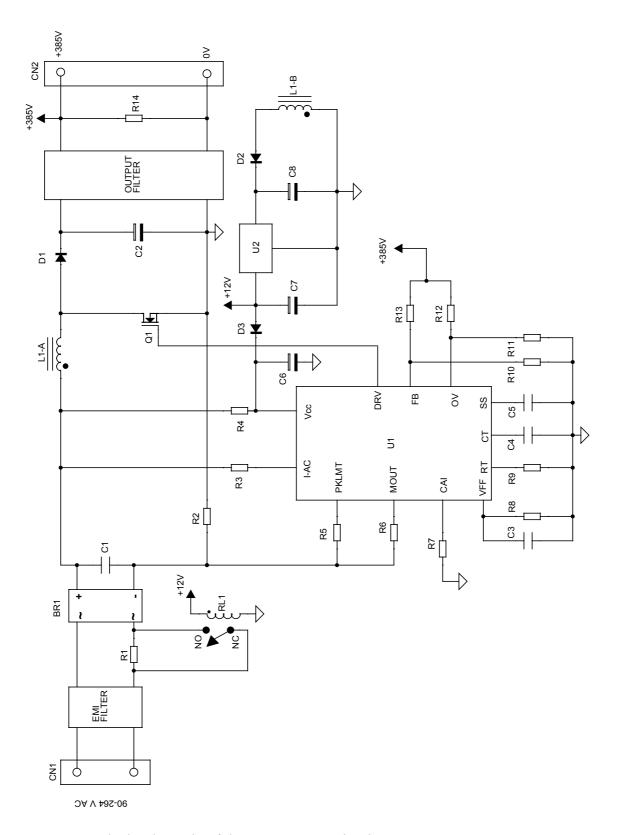

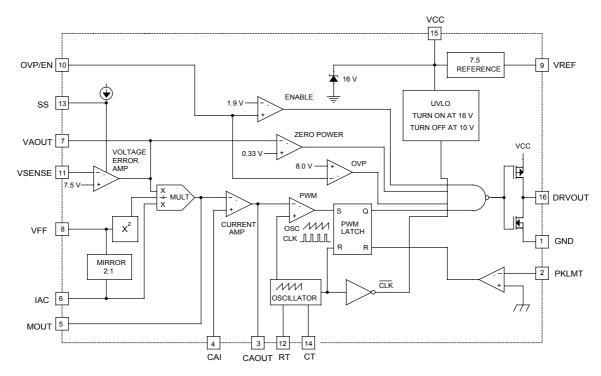

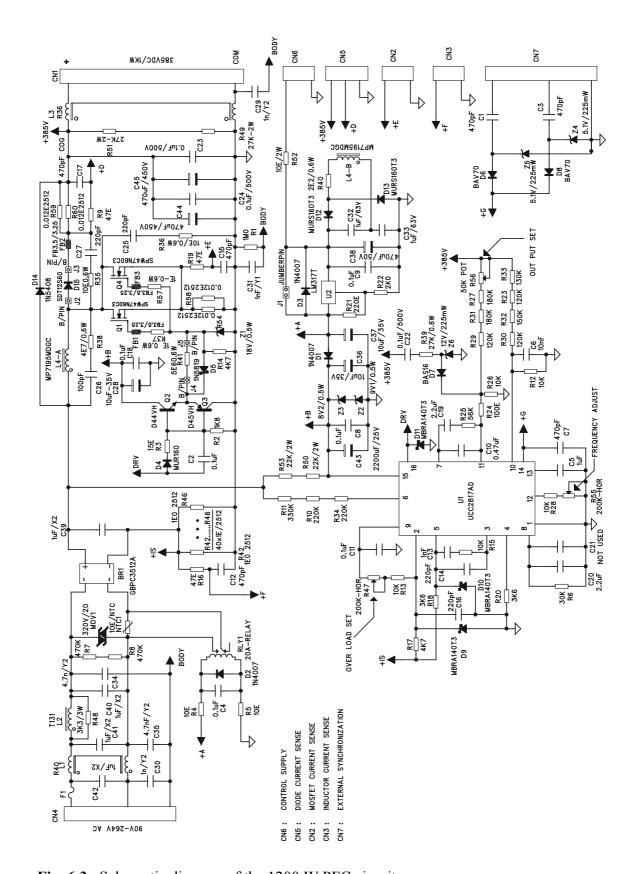

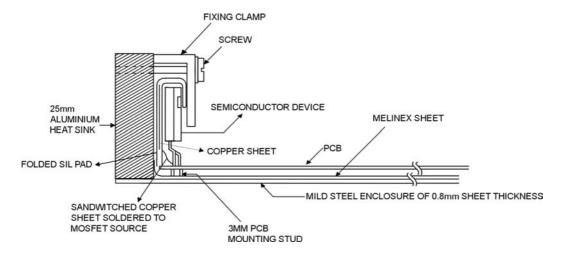

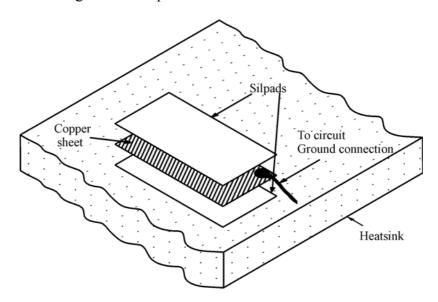

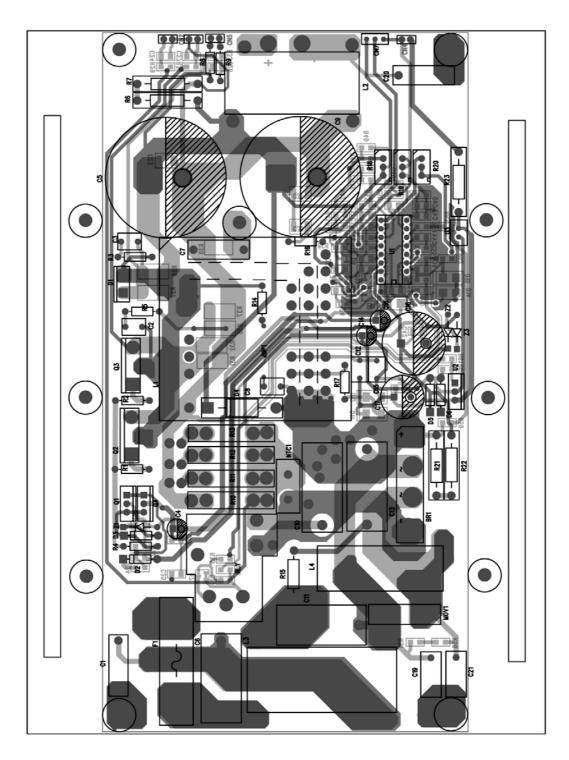

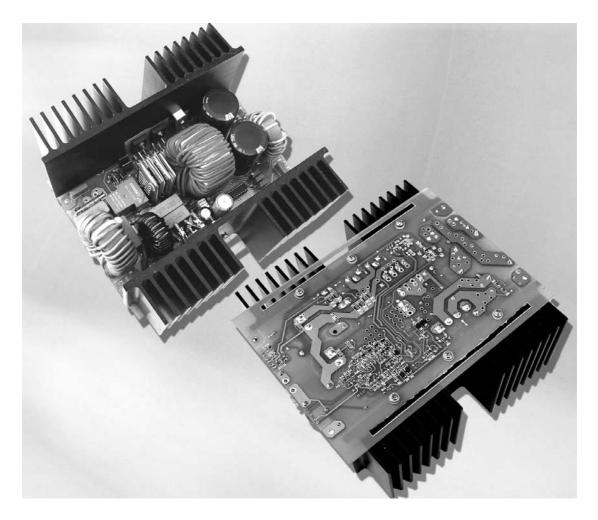

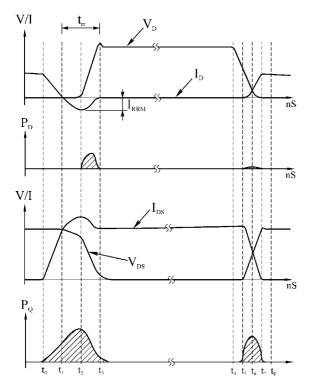

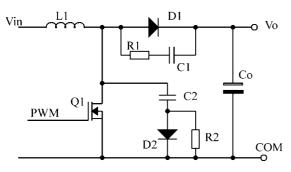

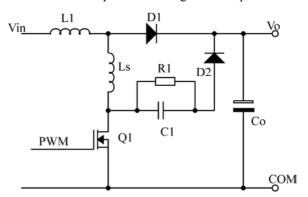

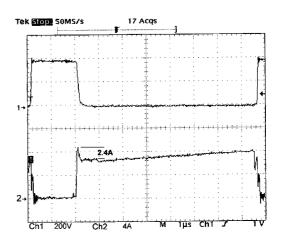

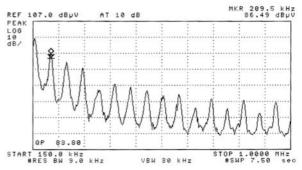

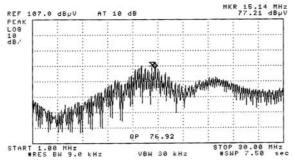

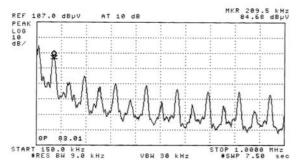

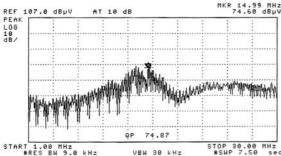

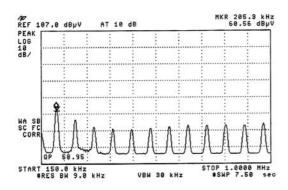

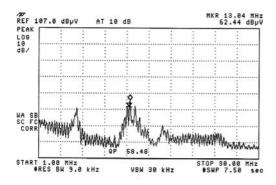

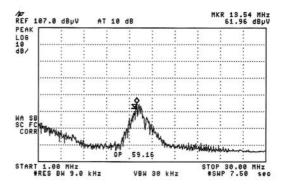

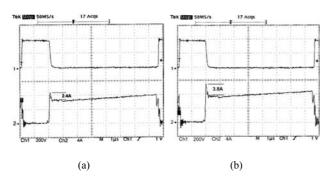

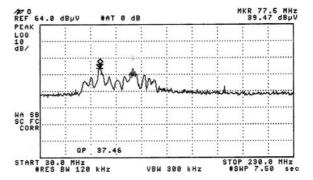

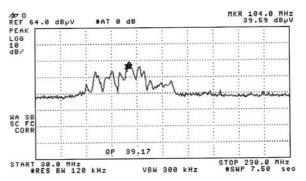

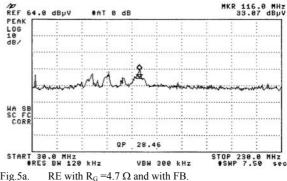

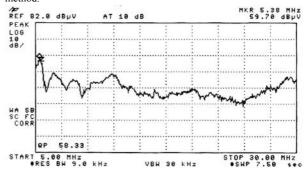

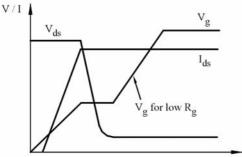

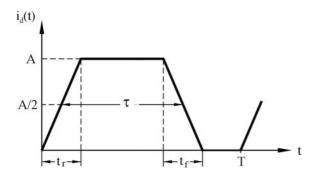

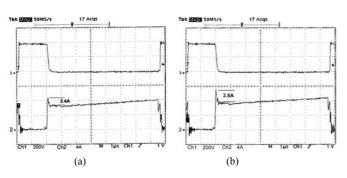

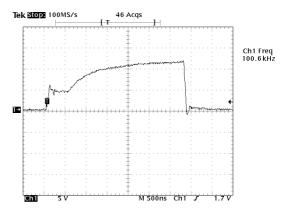

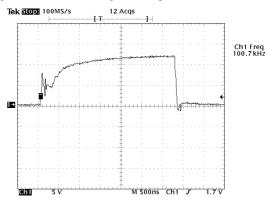

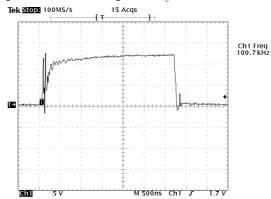

The net charge in the capacitor is found by integrating the above capacitor current waveform  $i_c(t)$ , over one switching period we have,